1 前言

不知道大家是否遇到过这种情况:在对接收机或者发射机进行仿真时,由于芯片中的时钟产生为一个 PLL,该 PLL 电路结构较为复杂,并且通常需要经过大量的时间才能够锁定,从而才能够产生我们所期望的时钟信号。但是,对于收发机而言,时钟信号是一个非常关键的信号,只有时钟信号正常产生后收发系统才能够正常工作。因此,在对整体系统进行仿真时,往往由于这个时钟电路的存在,从而导致在对收发机进行仿真时,需要大量的时间浪费在等待时钟稳定上。这往往是不能接受的。因此,需要找到一种能够加速仿真的方法,来对收发机链路进行快速仿真。

之前的一篇文章提到了在 Cadence 中可以将时域仿真保存为波形文件的形式,从而加快对系统的时域功能的仿真。但是,除了时域仿真外,收发链路通常还需要进行一些频域上的仿真,以此来确定收发链路的变频功能是否正常。在设计时通常会使用 HB 仿真或者 PSS 仿真来对收发链路进行频域仿真。但是,对于这些仿真器,如果使用之前文章中的设置,并无法成功仿真出电路功能的问题,接下来本文就对这一问题进行分析。

2 问题

2.1 分析用例

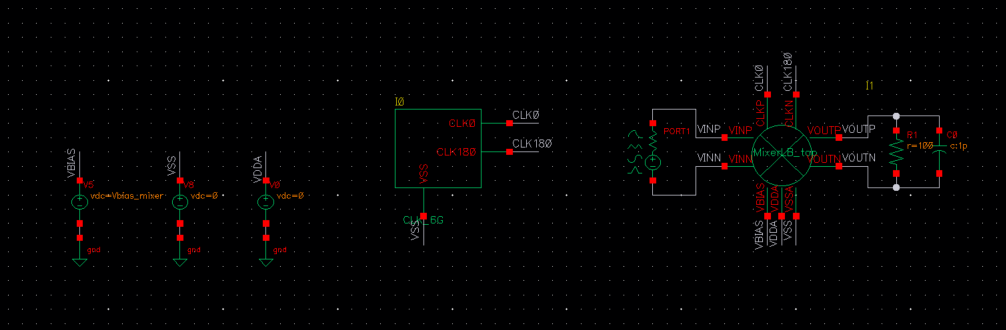

下面我们来看这样一个测试电路:

这个测试电路中存在一个混频器,而仿真电路的目标就是仿真出这个混频器的转换增益。该混频器的输入为一个 100 Ohm 的 PORT,输出接入到一个 100 Ohm 的阻抗匹配电组以及一个滤波电容上。

其中,”/I0″ 即为保存为波形文件形式的时钟源,它内部的内容为:

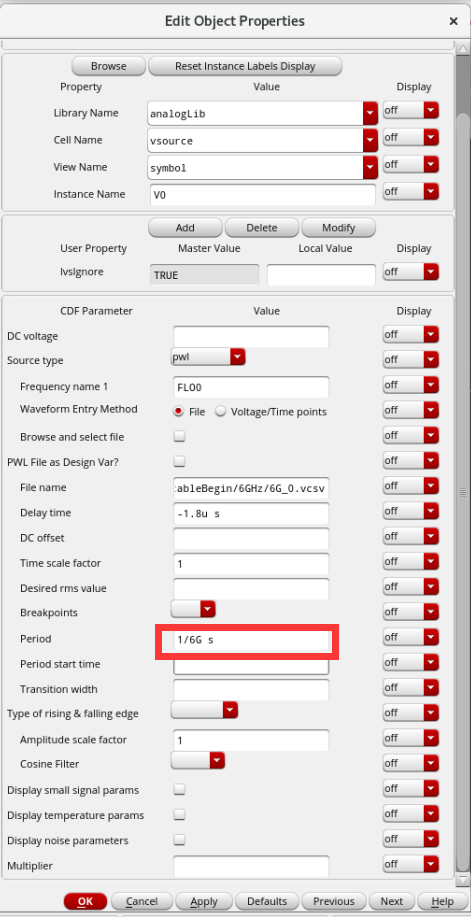

上图中的两个电压源内部即为波形文件,目前该电压源内部的设计为:

可以看出,该电压源中成功的导入了一个 6 GHz 频率输出的波形文件,也就是说本次仿真的系统本振频率为 6 GHz。

2.2 时域仿真

首先我们先看一下这种设置条件下的时域仿真结果。设置该电路进行 100 ns 的时域仿真,并 POLT 出两个时钟端以及输入输出端的电压波形如下图:

通过该波形可以看出,Mixer 的输出具有正常的下变频功能,能够将射频信号下变频到中频频率,由此说明时域仿真下电路功能正常。

2.3 频域仿真

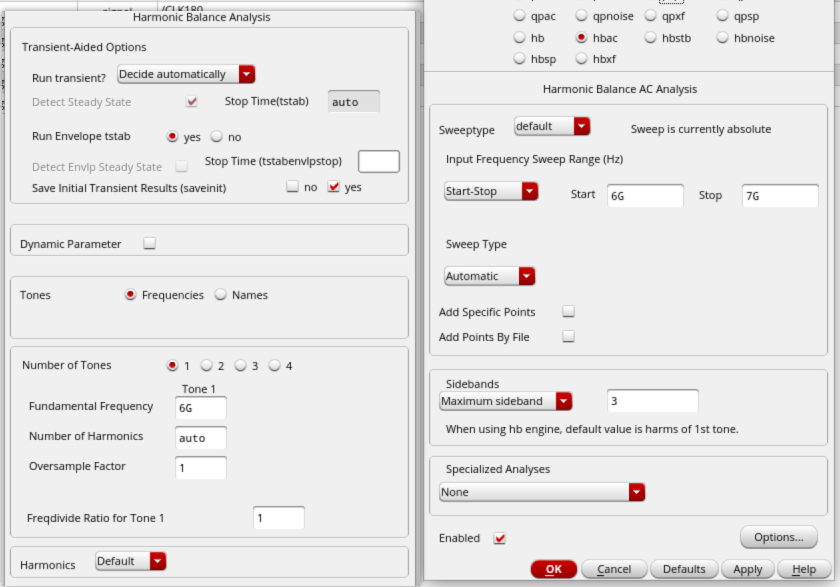

随后使用 HB 仿真器对该电路进行频域上的转移特性仿真。在仿真时将 HB 设置中的第一个 tone 设置为 6 GHz,并配置好 HBAC仿真器,如下图:

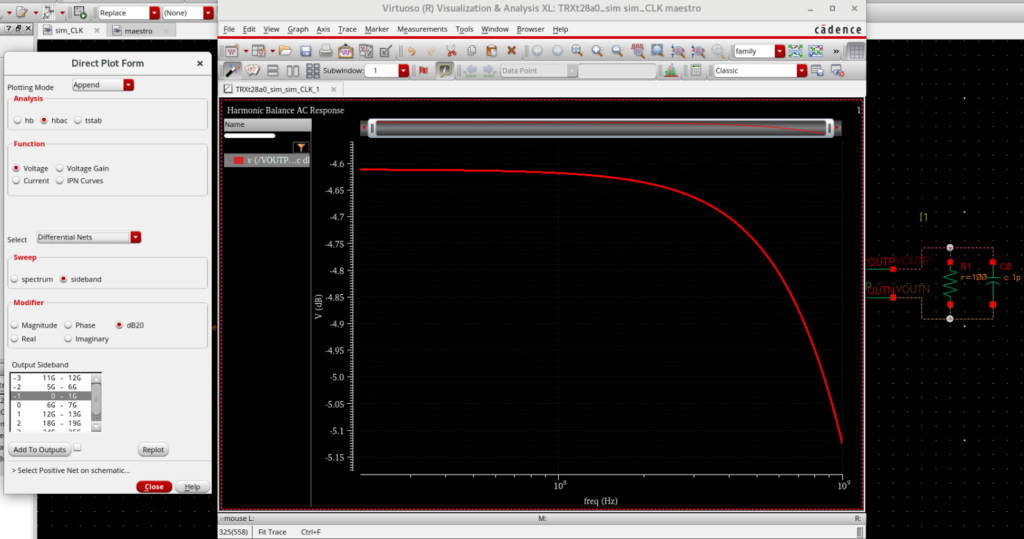

配置好后,即可进行电路转移特性的仿真。运行仿真后得到的转移特性仿真结果为:

可以看出,HB 和 HBAC 所提供的频域转移特性仿真结果达到了惊人的 -333 dB!这很明显与之前时域仿真的结果想冲突。那么,造成这个情况的原因是什么呢?

2.4 原因分析

在 HB 仿真中,我们不仅仅能够看到输出的转换增益,同时还可以看 HB 仿真器在求解谐波平衡前的时域仿真波形,以及 HB 仿真求解出来的各个点的稳态时域波形。

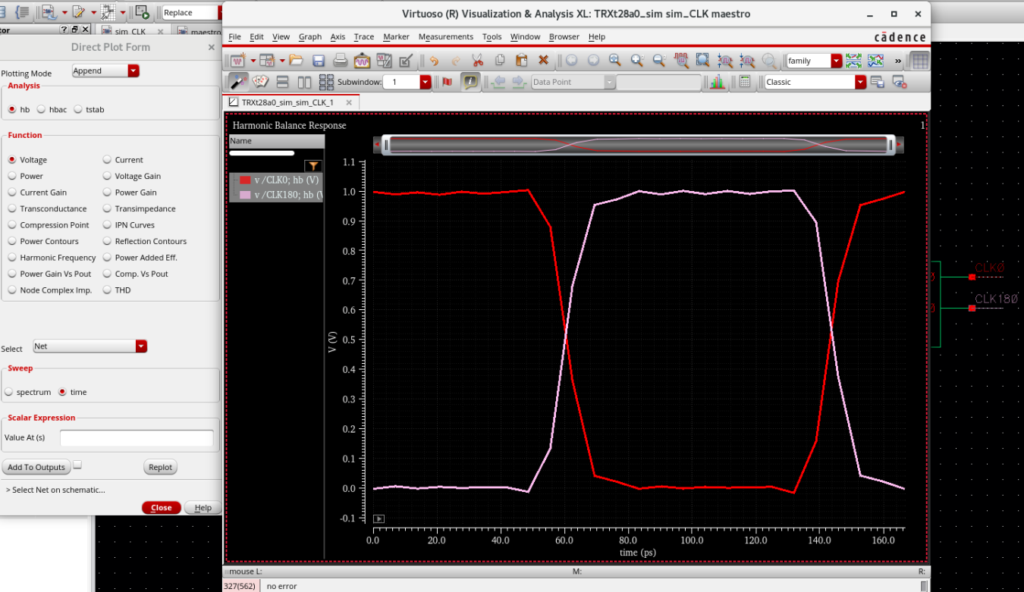

这里,我们选择输出 HB 求解出的稳态时时钟的周期波形,如下图:

可以看出,在 HB 的求解结果中,时钟是没有任何波形变化的,而是变成了一个恒定的 01 电平,这就是 HB 仿真器无法正确求解出转换增益的原因。

3 解决方式

对于这个问题,有一个非常简单的解决方式,就是可以通过设置产生波形文件的电压源,认为的赋予波形文件一个周期。当波形文件被赋予了一个周期后,HB 仿真进行求解时,就能够识别到波形文件这个周期信号,从而能够正常的进行谐波平衡分析,如下图:

通过使用这种设置方式进行上文中提到的 HB 仿真,最终得到的转移特性仿真结果为:

可以看出,此时 HB 和 HBAC 仿真就能够正常的输出一个带通特性的仿真结果了。

此时,使用 HB 仿真查看求解出的稳态时的时域波形,也可以发现通过这样设置后,HB 仿真已经能够正确的求解出稳态时的时钟波形了,而不是像之前一样只有一个 01 电平,如下图: