1 前言

在模拟集成电路设计中,对电路进行仿真是评估电路能否正常工作以及获知电路的具体性能参数的一个重要的方式。而对于一个特定的模拟电路结构而言,通常会存在数种不同的性能参数来描述电路的具体工作特性,并且某些电路中还会具有一些数字单元需要控制,此外在流片前通常还需要进行一些诸如工艺角和蒙卡之类的的仿真。对于一个模拟电路而言,通常需要运行数种不同的仿真才后才能对电路性能有一个比较全面的了解。这就导致该领域的新人在刚刚掌握仿真器的用法后,会对一个一个运行这数种仿真感到恐惧,同时一个一个运行也会导致大量的时间浪费。因此有必要找到一种能够快速并行的运行多种不同类型的仿真的操作方式,从而解放人的手工劳动,减少时间的浪费,将宝贵的时间利用在电路设计中去。本文将主要针对这一问题,介绍 Cadence Virtuso 中 maesrto 仿真平台下的快速仿真方法,从而达到白天配置仿真—>晚上服务器跑仿真->第二天「收菜」(获取并整理仿真结果)的高效仿真模式。

2 maestro 仿真平台介绍

目前模拟电路设计通常会在 Cadence Virtuoso 软件中进行。在该平台能够完成模拟芯片的原理图设计、前仿真、版图设计、后仿真等全流程。为了满足不同类型模拟电路的设计需求,Virtuoso 软件中提供了强大的仿真平台以及多种不同类型的仿真工具。早期的仿真环境主要包含 ADE L 和 ADE XL,但是在 Virtuoso IC617 版本后,Cadence 公司新推出了两款仿真工具 ADE Explorer 和 ADE Assembler,用于替代原本的 ADE L、ADE XL 以及 ADE GXL 环境。相比于原本的 ADE L 仿真环境,ADE Explorer 将单次仿真、corners、sweeps、蒙特卡罗以及参数对比等功能都整合在了 ADE Explorer 中,而 ADE Assembler 则主要取代了之前的 ADE XL 以及 ADE GXL 功能。

在创建 ADE Explorer 和 ADE Assembler 时,Cadence 给出的默认 View 名字是 maestro,因此这后续也用「maestro」来代指这两种环境。接下来本文将讲述一下 maestro 平台的使用方法以及一些能够提高仿真速度的使用技巧,争取能够使大家在看完这篇文章后,学会这种「收菜」式的仿真方式。

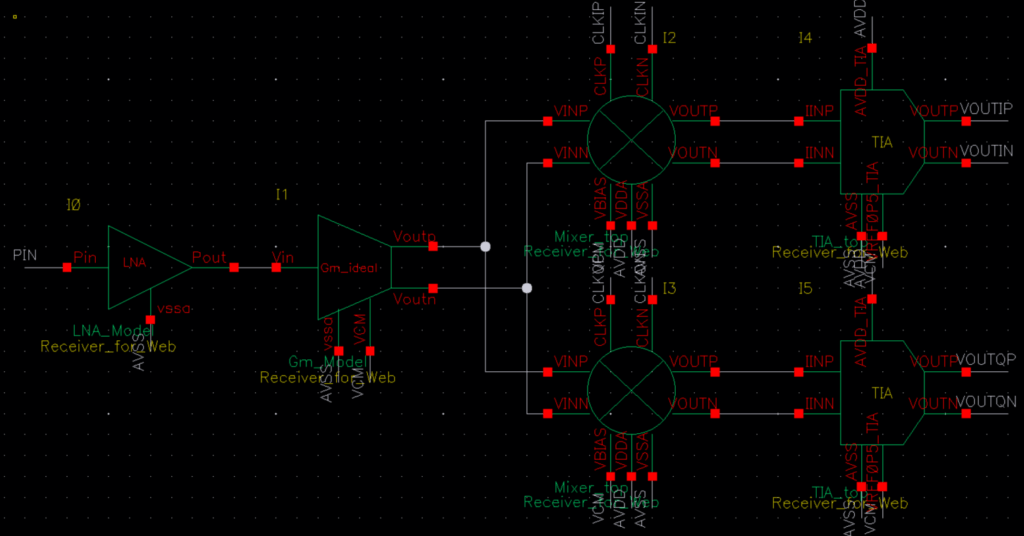

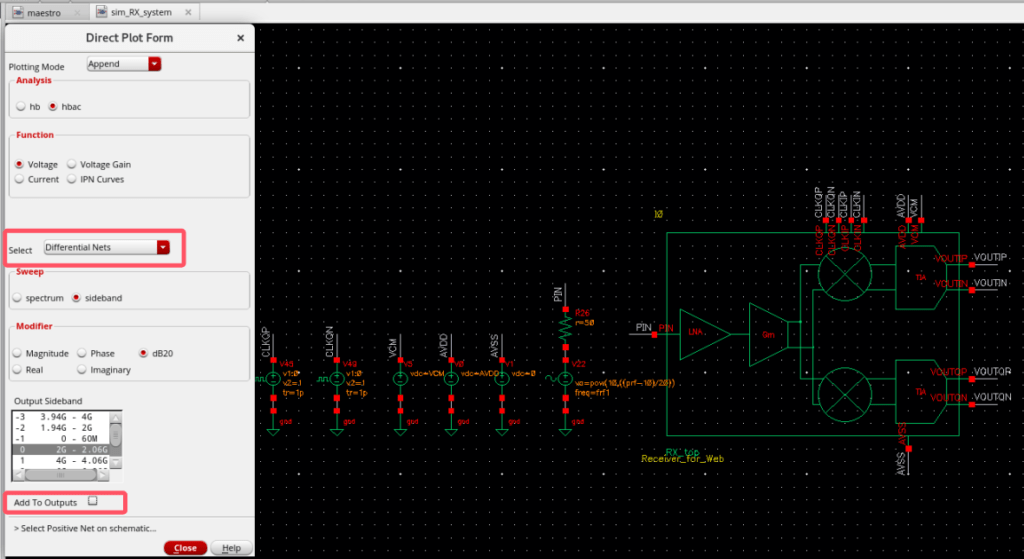

由于本人之前做过一定的射频接收机方面的工作,同时射频接收机需要仿真的指标参数众多,例如增益、带宽、输入匹配、噪声、线性度等等,比较适合用于介绍收菜式仿真,因此这里将使用一个如下图所示的常见的零中频结构的接收机来作为演示示例。注意,本篇文章中并不会具体介绍零中频接收机应当如何仿真,该接收机仅作为示例来演示如何使用 maestro 进行快速仿真,后续如有机会会单独出一期关于接收机如何仿真的介绍。

3 从一个简单的仿真开始——ADE Explorer

这一章将主要介绍一下 ADE Explorer 的使用方法。该工具主要用于替代之前的 ADE L,而由于大家一般对 ADE L 比较熟悉,可能有过一定的实际使用经验,因此这部分的内容也相对而言比较简单。这部分将主要介绍与 ADE L 用法相似的情况——如何使用 ADE Explorer 配置并完成一个仿真。

3.1 搭建好 Testbench

要进行仿真,首先就需要有一个 Testbench,因此进行仿真的第一件事情就是为自己的电路搭建一个合适的 Testbench。一个好的 Teshbench 需要正确模拟待仿真的电路所处的环境,以及输入和负载情况等等。这篇文章主要讲解仿真环境的使用方法,因此这里就先不把重点放在搭建 Testbench 的注意事项上,后续如果有机会会考虑单独出一个相关的教程。

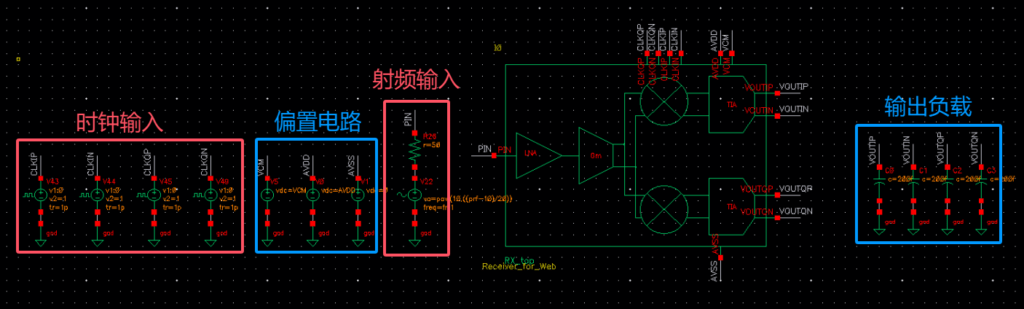

下图是我这边初步搭建好的一个 Testbench,主要包含输入信号、输出负载以及偏执电路三个部分。其中输入信号部分负责提供射频信号和时钟信号;输出负载主要用来模拟接收机后级电路的负载环境;而偏执电路则用来提供电源电压、共模电压等偏执。

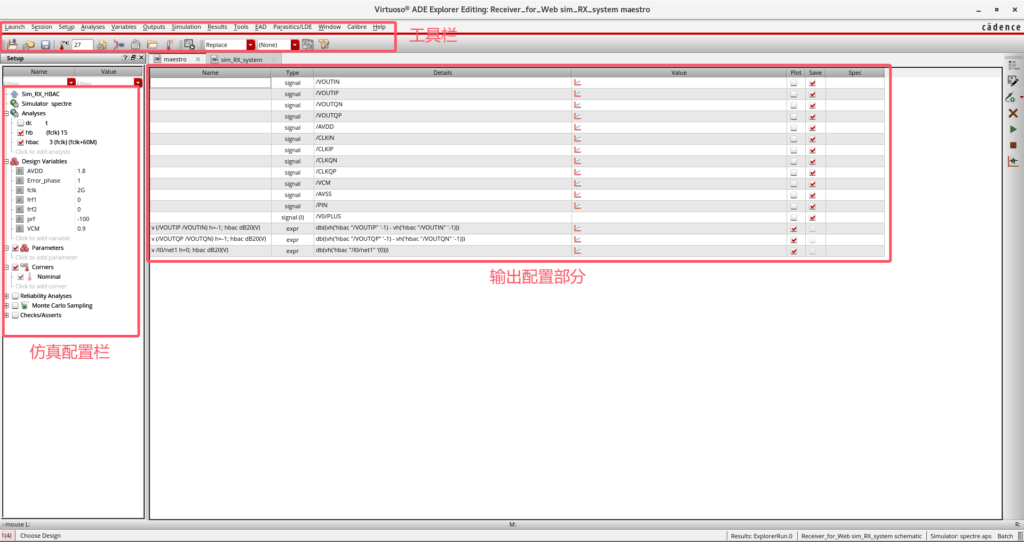

在搭建好 Testbench 后,在原理图的右上角选择「Launch -> ADE Explorer」,并选择「Create New View」即可新建一个 maesrto 的 View,并自动打开 ADE Explorer。ADE Explorer 的界面可以大体分为三个部分:右侧的仿真配置部分、左侧的 Outputs 配置部分和上面的工具栏,如下图。

3.2 使用仿真变量

在搭建 testbench 时,也需要设置好合适的仿真变量,以便于后续对电路的各种参数进行快速仿真。通常可以选择将外加的激励和偏置设置为仿真变量;此外也可以选择将一些感兴趣的电路参数设置为仿真变量。

3.2.1 在原理图中设置仿真变量

通常仿真变量可以在 virtuoso 原理图中「Q」快捷键打开的「Edit Object Properties」界面中直接设置,对于符合规则的字母数字以及特殊字符组合,virtuoso 会自动将其识别为变量,并且可以在仿真中使用。下面是个人总结的在设置变量时必须遵守的一些规则:

- 变量名由英文字母、下划线或数字组成,并且第一个字符必须是英文字母;

- 变量名不能是 Cadence 中的关键字,包括 skill 语言中的关键字和 spectre 语言中的关键字,例如:GND、capacitor、subckt、tran、ac;

- 变量名不能是各种电子元件的缩写、单位的缩写、用于表示数量级的缩写词及其大小写,例如:m、u、n、M1、m1、R1、Ohms;

- 变量名不能是大家目前所使用的工艺库中用于在 spice 网表中表示器件参数的缩写,例如:w、l、multi。

下面时个人建议的一些变量名设置规则:

- 变量名以字母开头,并且首字母建议大写;

- 变量名不要太过简洁(如「nf」,虽然看起来像是 Noise Figure 的缩写,但是在 tsmc28nm 工艺下会和工艺库中 MOS 晶体管网表中的 Number of Fingers 参数混淆),最好是三个及三个以上字符,以防止不经意间与一些 spectre 中的关键字混淆,从而影响仿真;

- 变量名要有实际含义,不要随便起一些看不出来意义的变量名;

- 变量名应使用英文单词或其缩写,避免使用拼音或中文;

- 由多个单词组成的变量名,每个单词首字母大写或者中间使用下划线分隔。

下面是一些个人喜欢的变量名,大家可以参考:

- 电源类:VDD, AVDD, AVDD1P8, AVDD_LNA, AVDD1P0_TIA;

- 地类:VSS, AVSS, DVSS, DVSS_SPI;

- 偏置电压类:VBias, VCM, VCM_0P9, VBias_LNA;

- 数字控制字类:EN, EN_LNA, Bias_CTRL, BW_CTRL, Gain_CTRL;

- 元器件参数类:R_1, R_s, C_c, Ceq, Laux, M_n1, L_p1;

- 激励信号类:flo, frf1, frf2, prf, plo, vp_in, Iin, Iac.

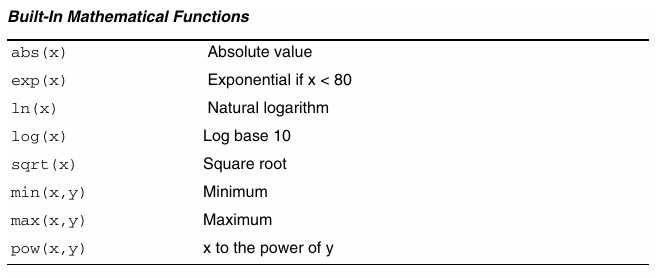

此外,在 Edit Object Properties 界面中设置变量时,也可使用一些 spectre 语言中内置的数学函数,virtuoso 会在仿真时自动识别,如下图。

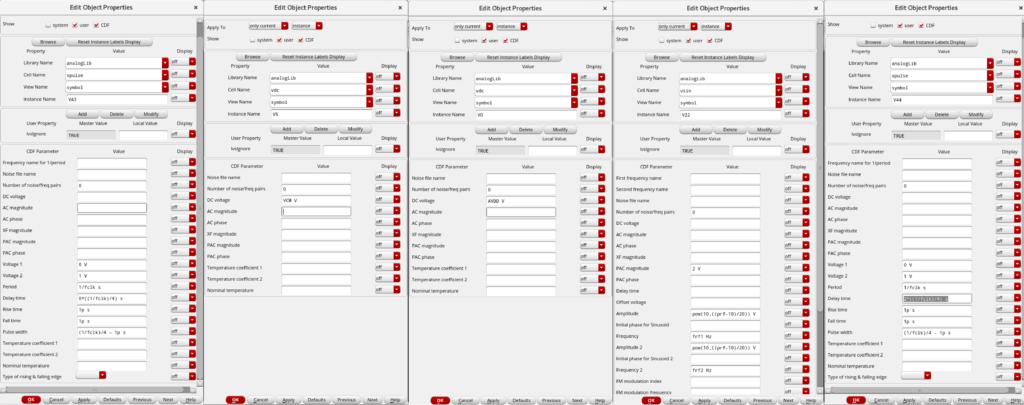

在这个接收机电路中,本人选择将偏置电路部分、输入部分以及一些能够有助于配置不同类型仿真的参数设置为了仿真变量,如下图所示。

其中 AVDD 用来提供整体接收机的电源电压、VCM 用来提供共模偏置电压、fclk, frf1, frf2, prf 则用来产生接收机的输入激励。

3.2.2 在 maestro 中使用仿真变量

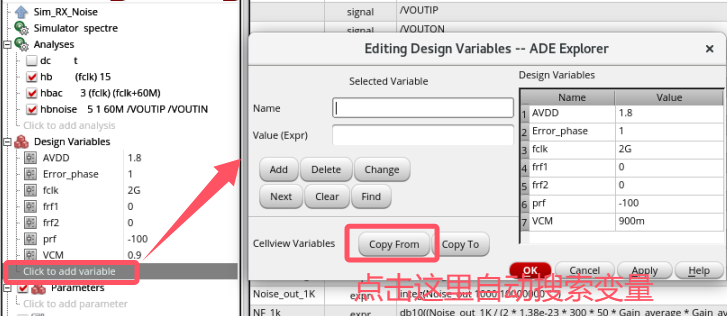

maestro 可以自动扫描识别并自动添加仿真变量,只需要在 ADE Explorer 的「Design Variables」中双击「Clecks to add variables」,然后再在弹出的界面中选择「Copy From」,即可自动从原理图中查找变量并列出。当然也可以使用手动添加的方式输入变量。

此外,由于「Copy From」搜索仿真变量的原理为将 schematic 中的所有调用的器件都过一遍,找到变量后将其放到「Design Variables」中,因此对于存在后仿真网表的电路图不要使用该功能搜索仿真变量!后仿真网表包含的器件数过多,直接使用该功能很可能会导致卡死。

双击「Design Variables」中的变量即可修改变量值。设置变量值时可以使用例如「1E-3」之类的科学计数法,以及「G, M, k, m, u, n, p, f」等表示数量级的结尾,从而更方便的设置变量值。

3.2.3 对仿真变量进行扫参操作

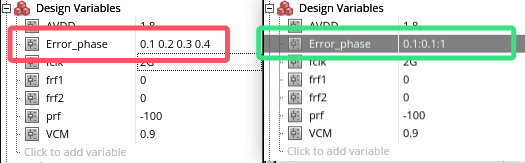

在「Design Variables」中也可以实现对某个变量的值进行扫参。具体的方法为在变量值里使用空格做分隔输入多个值,或者使用「初值:步进:终值」的方式进行输入,如下图。

完成后点击运行仿真,即可对该变量进行参数扫描。在运行参数扫描仿真时,maesrto 将以纵向并行运行的方式同时运行多个不同参数下的仿真。

3.3 选择仿真器

想要完成一个仿真,还需要选择好需要使用的仿真器,并且对它进行正确的设置,以确保仿真能够正确运行。这里并不会讲具体每种仿真该如何选择仿真器,以及具体每种仿真器该如何设置,而且会讲一下选择仿真器时涉及到的一些能够和仿真变量配合使用的特殊的设置方法。

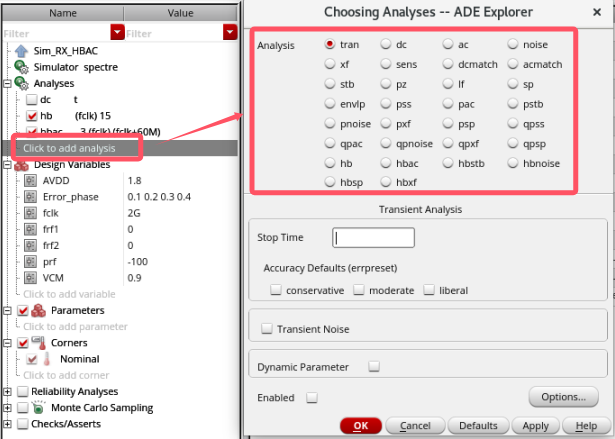

在「Analysis」中双击「Clecks to add analysis」,即可进入仿真器的选择和设置界面,如下图:

在设置界面中可以配置仿真精度、仿真参数等。例如对于时域仿真,只需要在其中输入好自己想要仿真的时长,并点击「Apply」或者「OK」就可以了。对于其他的仿真的设置方法也是类似的,选择好仿真后设置好参数就可以了。

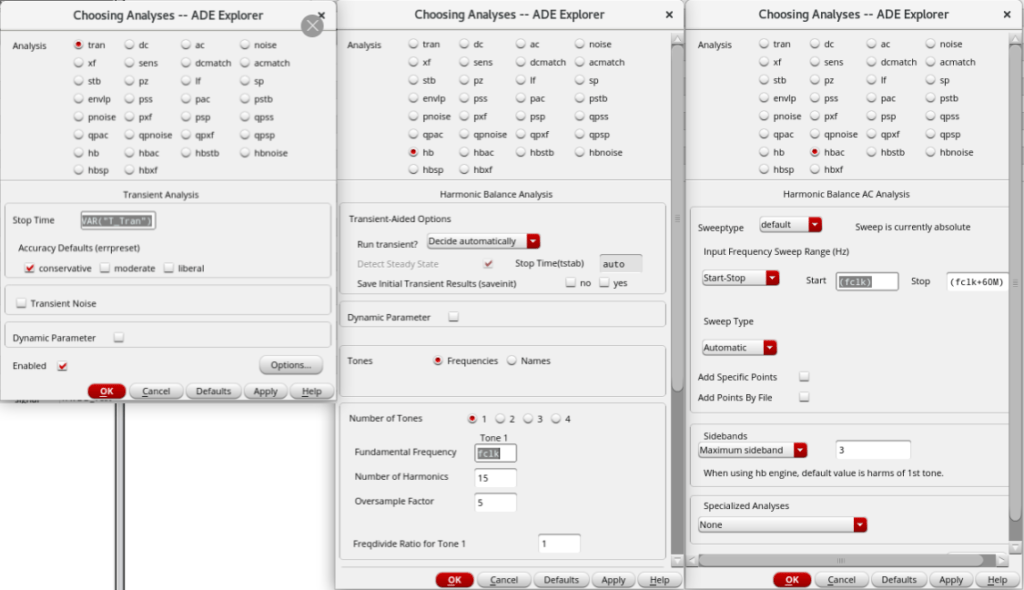

这里主要介绍一下配置仿真时的一种特殊用法——在仿真设置界面中是可以使用我们在「Design Variables」中设置的变量的。使用的方法主要分为两种,一种例如 tran 仿真,它的仿真时长参数无法直接使用我们设置好的变量,因此需要使用 VAR("变量名") 的方式来使用仿真变量,例如:VAR("T_tran");另一种是诸如 hb、pss、hbac、pac 等这一系列的仿真,这一系列的仿真的仿真参数中是可以直接使用大家设置好的变量的,因此只需要直接在仿真参数中输入变量名即可,如下图。

通过这样设置后,大家在进行仿真的时候,就可以通过改变变量值的来改变仿真参数了。这对接收机等这类需要覆盖不同频段的电路尤为友好。大家只需要根据自己想要仿真的本振频率修改一下 fclk 变量的数值,即可同时对应的修改仿真器中的仿真参数,而不需要我们进行修改仿真参数的操作,从而节省时间,并且能够与扫参以及工艺角等联动进行自动配置。

3.4 设置仿真输出(Outputs)

配置好要仿真器后,接下来的一个重要的事情就是选择仿真器保存的节点以及配置好仿真器的输出了。

3.4.1 选择保存的节点

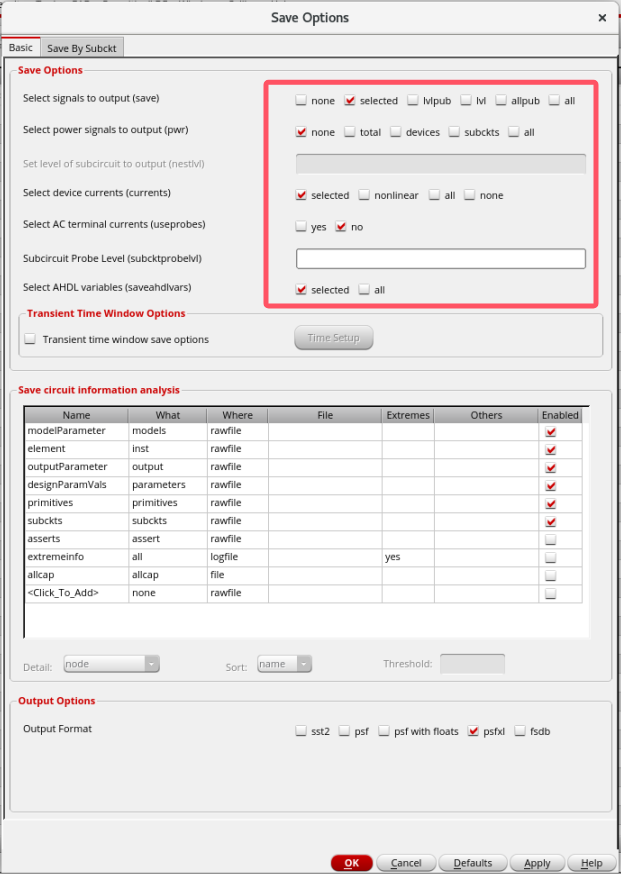

默认的情况下,仿真器会保存所有的「Net」电压值,而不会保存任何「Terminal」的电流值。默认保存的电压电流值可以在「Outputs -> Save All」中进行设置。

对于前仿真,由于网表中节点数通常较少,即使保存全部电压值也不会产生很大的储存空间占用,因此个人建议对于前仿真而言,可以使用默认的保存方案,并手动选择要保存的电流节点即可;对于后仿真而言,由于网表通常非常大、节点数很多,保存全部电压值会导致巨大的存储空间占用,同时还会拖缓仿真速度,因此建议保存方案按照下图中所示进行配置,从而使得仿真器只保存选择的电压和电流节点,随后对需要保存的电压和电流节点进行手动选择即可。

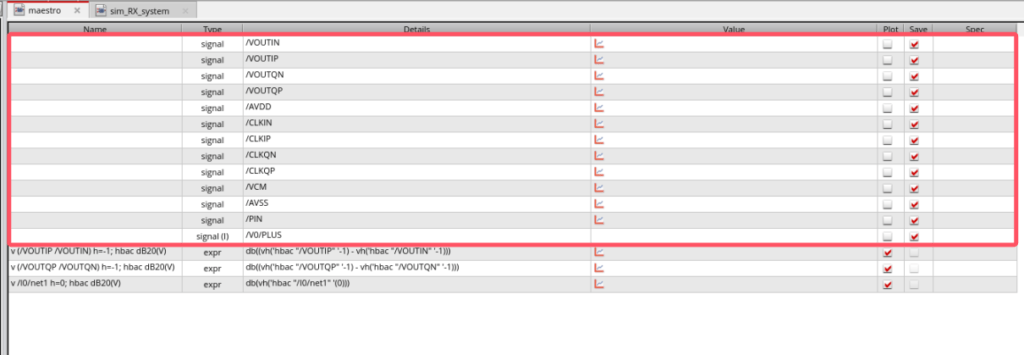

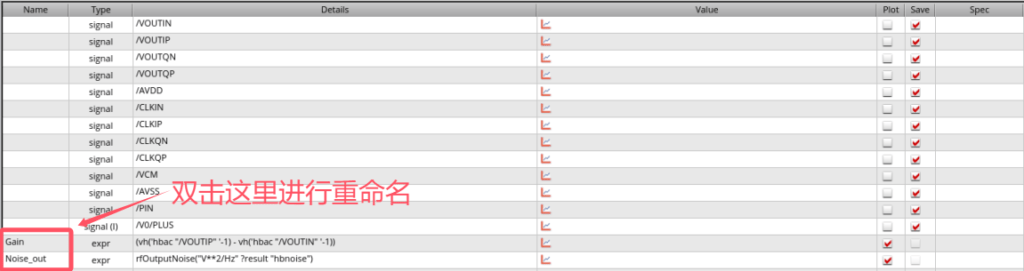

选择需要保存的电压和电流节点的方法为「Outputs -> To Be Saved -> Select On Design」,随后在原理图中选择要保存的电压和电流节点就可以了。被选择要保存的节点就会显示在 maestro 的输出列表中,如下图。

3.4.2 配置好仿真输出

通常一个待仿真的模拟电路会包含多个指标,除了这些指标外,通常仿真时还需要关注一些输出曲线,例如增益与频率关系曲线、输出与时间的关系曲线等等。因此,对于一个合格的「收菜」式仿真,我们就需要在「收菜」前就配置好这些要获取的仿真输出,从而在仿真运行完毕后能一键输出我们所关注的仿真结果,而不是一个一个的去通过繁琐的步骤去计算和查看,从而大大的加快仿真效率。

1)使用 Virtuoso 自带的输出配置

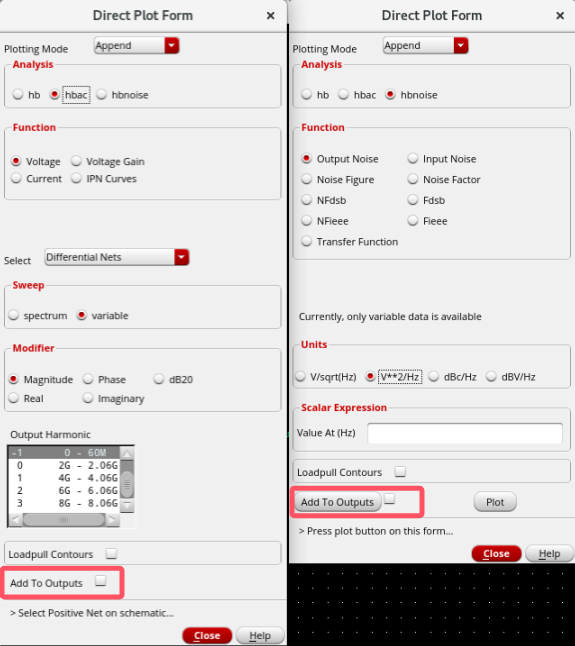

在配置仿真输出时,建议大家优先使用 Virtuoso 中自带的各种输出配置。这些自带的输出配置可以在运行完成仿真后查看。选择「Results -> Direct Plot -> Main Form」,即可自动跳转到原理图界面,同时出现「Direct Plot Form」的选择界面。在该界面中可以选择要输出的节点以及是否保存到 maestro 的 Outputs 中。勾选上「Add to Outputs」或者在 Plot 出图像后再单击「Add to Outputs」按钮,即可自动将该输出配置在 Outputs 中。

2)使用计算器与函数

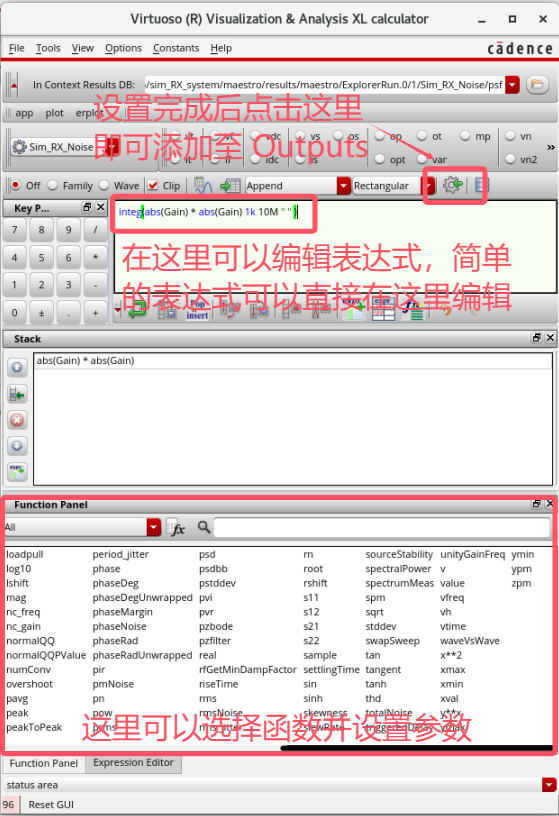

通常 Virtuoso 自带的输出配置可以覆盖绝大部分情况,尤其是一些比较复杂的输出情况,Virtuoso 基本都有自带的配置。但是对于一些特殊的指标比如两相时钟之间的相位差、增益曲线的 Ripple 等等情况,以及需要对多个指标进行数学计算从而得出另一个指标的情况(例如 FoM 值),自带的仿真配置中是无法覆盖的。这时候就需要用到 Virtuoso 中的计算器和计算器中自带的一些函数功能了。下面我将用一个仿真并手工计算接收机的噪声系数的例子来说明:

对于接收机而言,噪声系数的计算公式为,

$$ \mathrm{NF}=\frac{1}{2kTR_S}\frac{\overline{V_{n,out}^2}}{A_v^2}. $$$\overline{V_{n,out}^2}$为输出噪声功率谱密度,$A_v^2$为电压增益。因此只要仿真出接收机的电压增益以及输出的噪声功率谱密度即可计算出接收机的噪声系数。由于接收机通常是有一定带宽的,为了表征带宽内平均的噪声系数,可以对仿真出来的增益和输出噪声对带宽取平均值后带入表达式中进行计算。

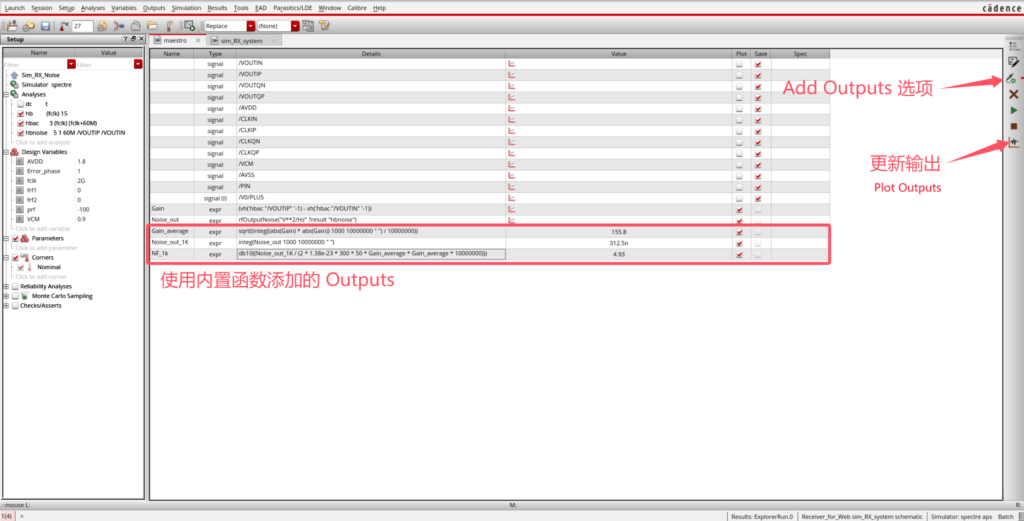

对于电压增益和输出噪声功率谱密度,可以使用 hb + hbac + hbnoise 仿真(或者 pss + pac + pnoise 仿真)得到。设置好仿真后并运行,随后选择「Results -> Direct Plot -> Main Form」即可获得增益随频率以及输出噪声随频率的曲线,并将其添加到 Outputs,如下图。

将这两条曲线添加到 Outputs 后,大家可以转到 ADE Explorer 中对这两条曲线进行重命名为 Gain 和 Noise_out,如下图。

这里进行重命名的原因是因为在 ADE Explorer 中是可以使用输出的 Name 来代替整个输出表达式进行运算,从而简化后续的操作。完成这一步后,就可以打开计算器并使用函数进行计算了。选择「Tools -> Calculator」即可打开 Virtuoso 中自带的计算器程序。按照下图所示的操作,将计算器中的内容编辑为 sqrt(integ(abs(Gain) * abs(Gain) 1k 10M " " )/10M),添加到输出即可计算出平均增益。可将其重命名为 Gain_average。

对于平均输出噪声功率密度,也可以如法炮制,使用计算器通过内置函数得到 integ(Noise_out 1k 10M " ") 的表达式即可。最后就是计算噪声系数,同样可以使用计算器,或者也可在 ADE Explorer 中直接使用右侧的「Add Outputs」选项新建一个 Output,并输入 db10((Noise_out_1K / (2 * 1.38e-23 * 300 * 50 * Gain_average * Gain_average * 10M))) 表达式即可。全部完成后点击右侧`Plot Outputs`选项即可显示出噪声系数的计算结果。最终的效果如下图所示。

除了上面提到的计算器中的函数外,maestro 的 Outputs 中还可以使用 Cadence Skill 语言中自带的函数,例如 modf(a b) 的取余函数以及 VAR("变量名") 这个获取变量值的函数。下面是使用 VAR("变量名") 函数的一个例子:

现在假设这样一种仿真场景:目前待仿真的电路为一个时钟生成电路,向其输入一个特定频率的信号后,它能够在不改变输入频率的情况下产生 0° 和 90° 正交的时钟输出。现在仿真的目的是得到这两相位时钟之间的相位差,并与 90° 进行相减,从而判断输出之间存在多大的相位误差。仿真使用时域仿真,时域仿真的时长由 T_tran 这个变量决定,目前这个变量的设定值为 20us。下面是一个较完整的 Phase Error 的输出表达式,

((triggeredDelay(VOUT0 VOUT90 0.5 "falling" 0.5 "falling" ?multiple nil ?nth ((VAR("fin") * VAR("T_Tran")) - 100)) * VAR("fin") * 360) - 90) 。

其中 VOUT0 为 (vtime('tran "/I0/VOUT0") - vtime('tran "/AVSS")) ,用于获取 0° 的时钟输出波形; VOUT90 为 (vtime('tran "/I0/VOUT90") - vtime('tran "/AVSS")) ,用于获取 90° 的时钟输出波形,`fin` 为一个仿真变量,决定输入时钟电路的信号频率;triggeredDelay() 函数用于计算两个波形在某个下降沿处的延时差;(VAR("fin") * VAR("T_Tran")) - 100 这个表达式用于选择倒数第 100 个边沿,以避开初期的不稳定状态。

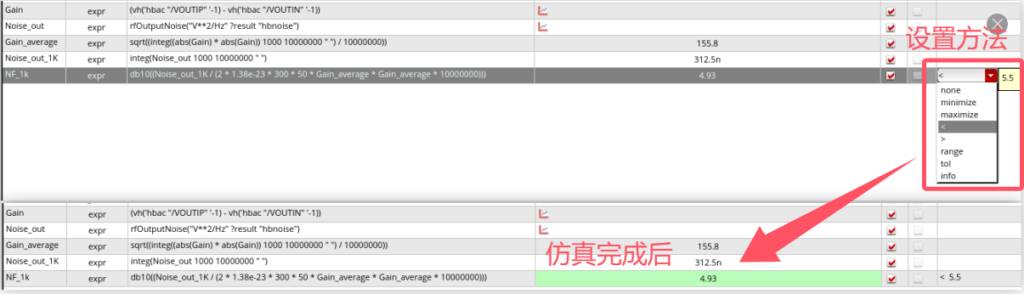

3.4.3 设置输出的 Spec

ADE Explorer 的 Outputs 可以设置输出的 Spec,这对于有明确指标要求的情况下对电路进行设计的应用场景下来说非常方便。添加 Spec 的方法为在添加的 Outputs基础上,在「Spec」一栏选择对应的限定条件,并输入限定数值即可。此时仿真输出后即可自动判断是否满足指标要求,满足会使用绿色显示,不满足会使用红色显示,如下图。

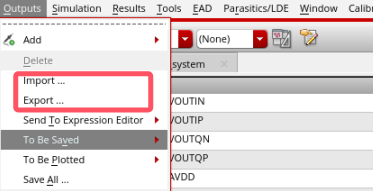

3.4.4 Outputs 的导入与导出

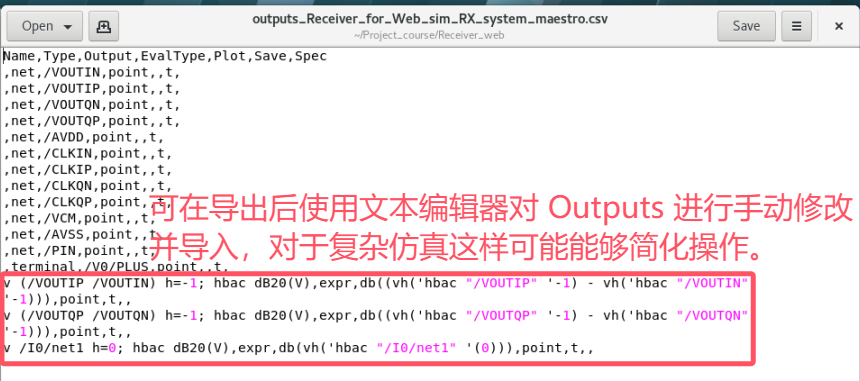

ADE Explorer 中的 Outputs 可以导出成 csv 格式的文件,也可以导入 csv 文件进行快速 Outputs 配置。通过导入与导出功能可以备份输出配置,也可以在多个不同的 maestor 中快速共享 Outputs 配置,从而减少配置 Outputs 所需要的时间。导入导出功能可以在「Outputs -> Import」和「Outputs -> Export」中找到,如下图。

导出后的 Outputs 文件是一个 csv 格式的文件,该文件中第一行标注了每列代表的信息,各列之间使用逗号进行分隔。该文件是可以使用文本编辑器(如 gedit、vim、VScode 等)打开并进行编辑修改的(编辑时需要注意好格式)。编辑后的文件可以再次导入 maestro 更新仿真 Outputs,如下图。

3.5 配置工作角 (Corners)

通常一个电路会在多种不同的条件状态下工作,例如在不同的温度、电源电压、工艺角下。此外,如果电路存在数字控制功能,那么芯片还会工作在不同的数字控制字状态下。在 maestro 中可以使用 Corners 功能来对电路的不同工作状态进行配置。

3.5.1 使用 Verilog-A 修调控制字

对于数字控制功能,可以使用 Verilog-A 代码并配合仿真变量的方式,实现通过使用仿真变量的方式修改数字位控制字的功能。具体的使用方式可以参考这篇文章:数模IC仿真技巧:用Verilog-A配置电路修调控制。

这篇文章中给出了实现 8bit 数字控制字的 Verilog-A 代码,其他的比特数可以通过修改代码中的位数、满摆幅值以及循环次数的方式实现,下面给出 16bit 数字控制位的代码以供参考

// VerilogA for npt28a0_model, model_ADC, veriloga

`include "constants.vams"

`include "disciplines.vams"

module model_ADC_16bit(out);

parameter real vdd =1;

parameter real vss =0;

parameter real trim =0 from [0:65535];

localparam integer full_scale = 65536;

output [15:0] out;

voltage [15:0] out;

real sample,thresh;

genvar i;

analog begin

sample =trim;

thresh =full_scale/2;

for (i=15;i>=0;i=i-1)begin

if (sample >=thresh)

begin

sample = sample-thresh;

V(out[i]) <+vdd;

end

else V(out[i]) <+ vss;

sample=2*sample;

end

end

endmodule如果需要实现 32bit 及以上的数字控制位,直接在上述代码下修改是无法使用的,这是因为 integer 变量的最大存储位宽是 32bit,因此如果直接修改会导致溢出从而影响功能。对于 32bit 及以上的控制字位数,这里需要使用 real 类型的变量。相关代码如下。

// VerilogA for npt28a0_model, model_ADC, veriloga

`include "constants.vams"

`include "disciplines.vams"

module model_ADC_32bit(out);

parameter real vdd =1;

parameter real vss =0;

parameter real trim =0 from [0:4294967295];

localparam real full_scale = 4294967296;

output [31:0] out;

voltage [31:0] out;

real sample,thresh;

genvar i;

analog begin

sample =trim;

thresh =full_scale/2;

for (i=31;i>=0;i=i-1)begin

if (sample >=thresh)

begin

sample = sample-thresh;

V(out[i]) <+vdd;

end

else V(out[i]) <+ vss;

sample=2*sample;

end

end

endmodule3.5.2 使用 Corners 功能配置电路工作状态

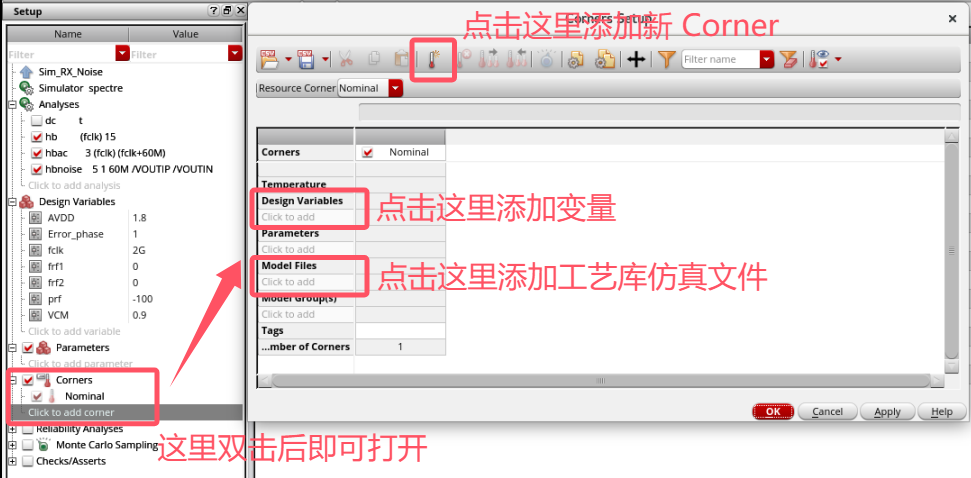

设置好仿真变量后,就可以使用 Corners 功能来对电路的不同工作条件进行配置了。在 ADE Explorer 的右侧边栏「Corners」下双击「cleck to add corner」,即可打开工艺角配置面板,随后就可以改变温度、工艺角以及仿真变量值,如下图。

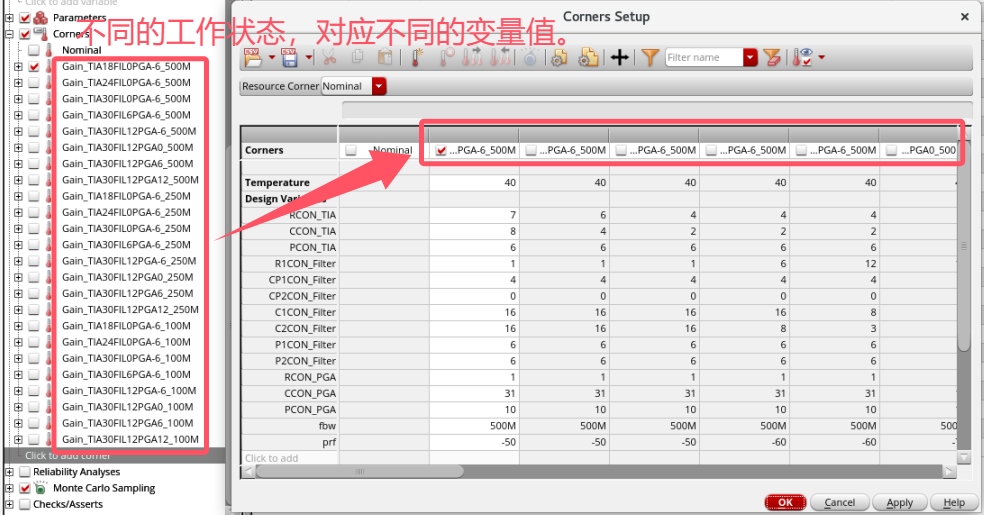

下图是一个使用 Corners 功能配置实现电路的多种不同的工作状态的一个示例。通过配置寄存器的控制字的 0, 1 数值,即可控制电路工作在多种不同的增益和带宽下。

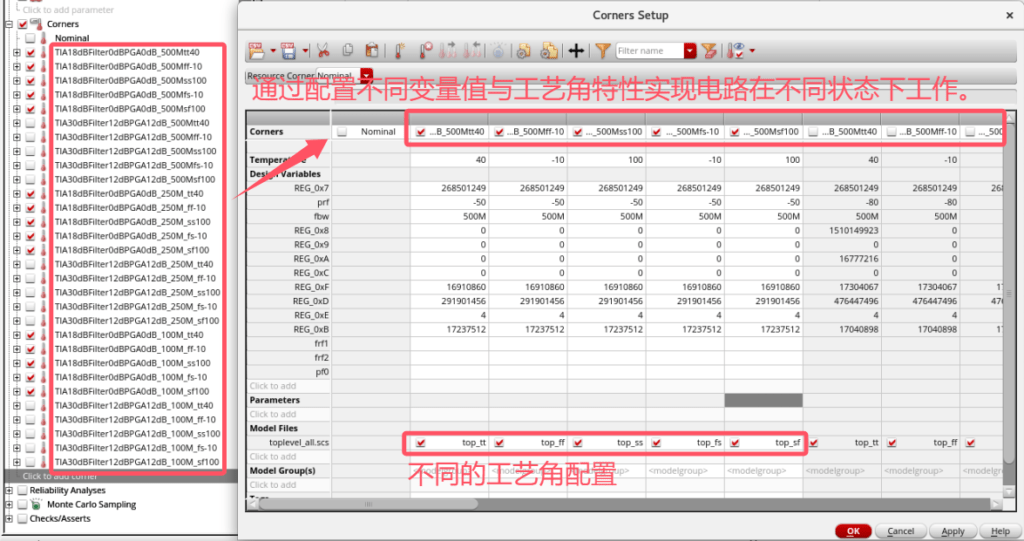

下图是一个使用 Corners 功能实现电路工作在不同的增益、带宽以及工艺角下的实例。通过这样配置即可对电路在不同增益带宽以及不同工艺角下的性能进行完整的验证。

学会了本节的配置方法后,大家如果想对于一个具有多个数字控制字同时需要验证多种工艺角下工作的电路进行便捷仿真的话,只需要白天的时候在 Corners 中录入好不同工作状态下的变量值以及工艺角特性,并给不同的 Corners 起上一个具有良好可读性的命名;随后下班前大家配置好仿真设置与仿真输出并勾选好自己想要进行仿真的工艺角,然后直接让服务器工作一晚上就可以了。如此操作就可以实现第二天上班时的仿真结果「收菜」了。

3.5.3 使用 Corners 进行参数或 PVT 扫描

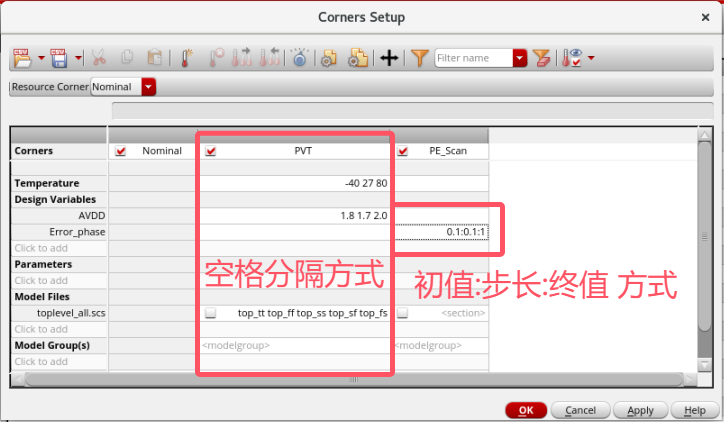

和设置仿真变量时一样,使用 Corners 同样可以进行参数扫描功能。Corners 同样具有两种参数扫描方法,一种是使用使用空格做分隔输入多个值,另一种是使用「初值:步进:终值」的方式进行输入,如下图。

完成后点击运行仿真,即可对利用 Corners 进行参数扫描。此时maesrto 将以横向并行运行的方式同时运行多个不同参数下的仿真。

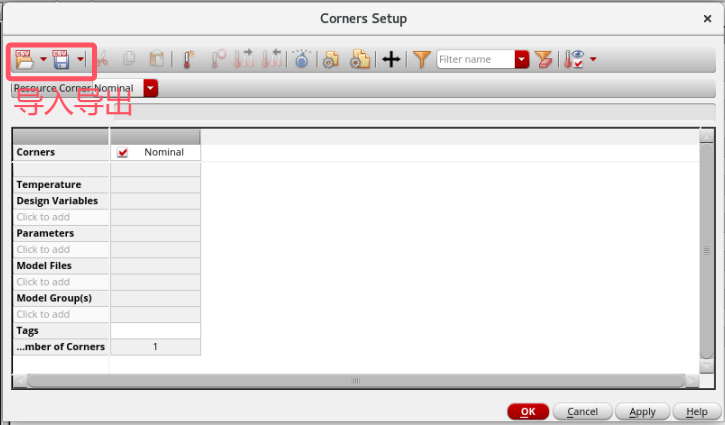

3.5.4 Corners 的导入与导出

与 Outputs 相同,Corners 是同样可以进行导入和导出的。具体的导入和导出的方式如下图。导入和导出的文件同样是一个 csv 文件,因此也可以使用文本编辑器打开,并在手动进行编辑后重新导入。

3.6 并行运行多个仿真

不知道大家在之前使用 ADE L 跑仿真扫参或者使用 ADE XL 跑工艺角时时有没有过这种想法,就是如果可以同时并行运行多个仿真就好了,这样就能快速的把所有情况扫完。事实上,这个操作在 maestro 中是可以实现的。

3.6.1 设置单个仿真占用的进程数

不过,在进行并行仿真前,需要先明确一个你的服务器的 CPU 最多能够支持多少线程。可以使用 cat /proc/cpuinfo| grep "processor"| wc -l 命令来查看该服务器总共具有的线程数,并记下该数值。该数值决定了你的服务器能够最多同时并行运行多少个仿真。

此外,还需要固定一下一个仿真占用的 CPU 线程数。如果不进行固定,则一个仿真可能会根据仿真大小占用 1-8 个线程不等,大型仿真占用的可能会更多。因此,为了更好的规划 CPU 的使用,最好让每个仿真都能有一个明确的线程占用数量。

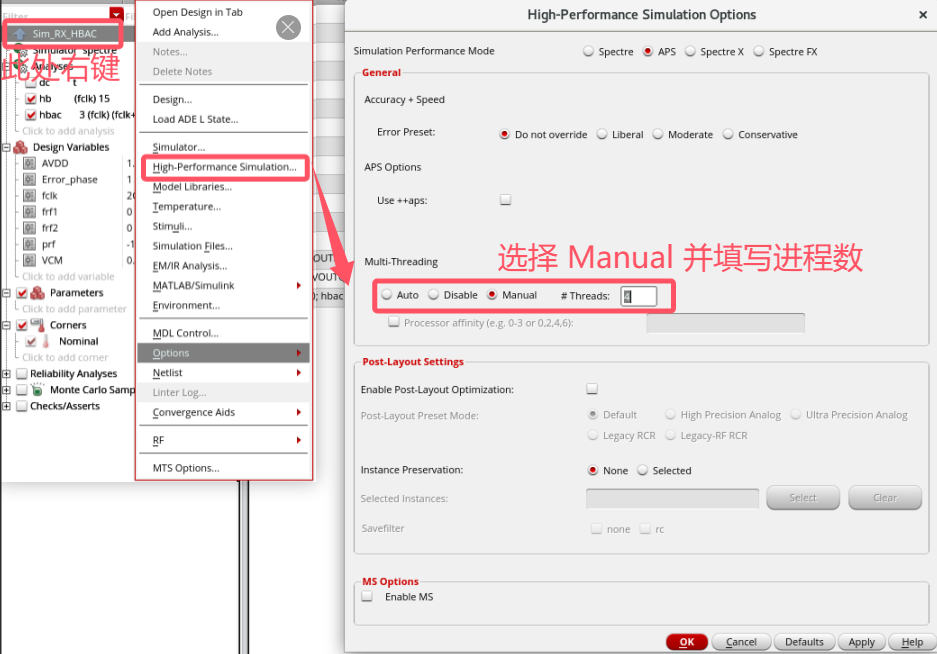

具体的设置方法为在 ADE Explorer 名字上右键,选择「High-Performance Simulation」即可打开进程数设置界面(或者「Setup -> High-Performance Simulation」也可打开)。在界面中「Multi-Threading」处设置为「Manal」,并输入进程数即可,如下图。通常小型仿真(例如模块级别电路的前仿真)设置占用 2 个线程就够了,大型仿真(系统级别的电路或者后仿真)可以设置占用 4 个或者 8 个线程。

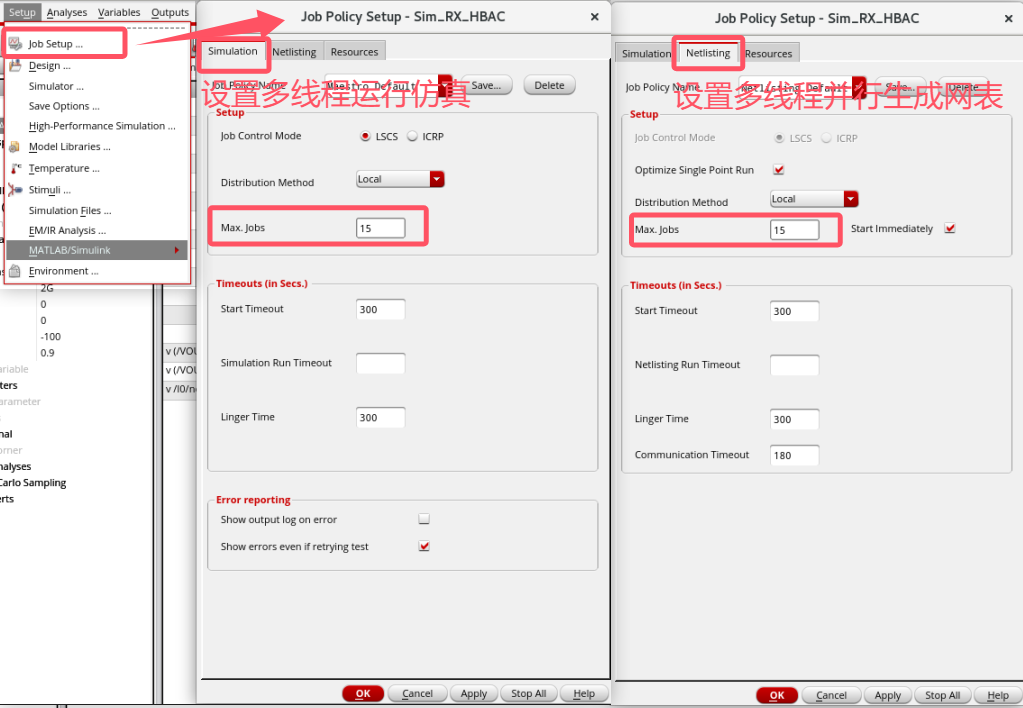

3.6.2 并行运行仿真

固定好每个仿真占用的线程数后,就可以开启并行仿真了。开启的方式在「Setup -> Job Setup」,并在打开的界面中的「Max.Jobs」处输入最大并行运行的仿真数值即可,如下图。然后点击「Apply」后就可以成功的开启并行仿真了。此外「Job Setup」还可以设置多线程并行生成网表,操作是类似的。

但是,事实上并行运行仿真的设置并不是随便输入一个数值这么简单,这个数值是有讲究的。如果输入的数值太大超出了 CPU 所能承受的最大数量,那么可能会导致仿真错误等等。因此下面讲一下并行数量该如何设置。

之前我们使用了指令查询了服务器中 CPU 的最大线程数,这里假设为 m;同时还固定了每个仿真占用的线程数,这里假设为 n。有了这两个数据就可以得出最大能并行运行的仿真数了。计算的方法相当于一个小学应用题:你的 CPU 一共 m 个线程,每个仿真占用 n 个线程,那么最大能同时跑几个?

很明显,这个问题的答案是 m/n。但是,经过本人的实际验证,个人建议的较优答案是 m/n-1(如果每个仿真固定占用的进程数小于 2 的话,为 m/n-2)。假设你的服务器一共有 64 个线程,每个仿真固定占用 4 个线程,那么最好的同时并行仿真数量是 15 个,而不是 16 个。

这样做的原因可以用资本家压榨牛马的方式来通俗理解:一个大资本家(maestro)想要压榨牛马(服务器)进行大量体力劳动,那么是不能把牛马每天的时间完全安排满的,这样的话牛马会过劳累死。所以必须要留下来一点喘息的余地以确保更长时间的可持续性压榨。科学一点的讲就是如果整个服务器 CPU 全占满了,那么及其容易发生崩溃卡死的情况,所以需要留下几个线程用来给一些正常运行的程序例如 linux 必要程序、virtuoso、top 之类的一个空间,确保服务器不会卡死。

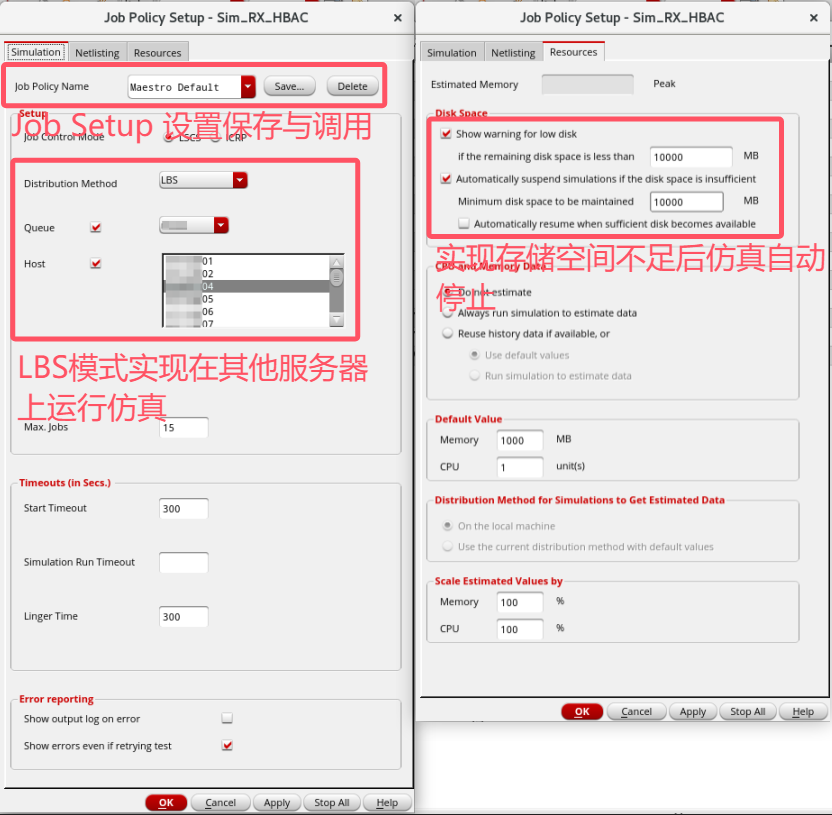

3.6.3 Job Setup 的其他妙用

除了上面提到的之外,「Job Setup」还有很多其他的妙用,如下图。大家可以将「Job Setup」的配置保存成一个文件,后续可以调用这个文件恢复配置;对于有大量服务器集群的情况,如果服务器管理员进行了配置,那么可以实现在一个服务器上运行 Virtuoso,而在其他服务器上跑仿真的功能;此外还可以设置当硬盘存储空间不足时自动暂停仿真,以防止因为空间不足导致的大量仿真停止。

3.7 配合 config 运行后仿真

在运行仿真时,大家可能会遇到一个 symbol 中存在多个原理图的情况,例如一个电路存在多个版本、存在后仿真时提取的「calibre」原理图以及 EMX 提取出来的「schematic_nport」等等情况。这种情况下就需要使用 config 来切换某个 symbol 在仿真时使用的原理图。

3.7.1 使用 config 切换原理图

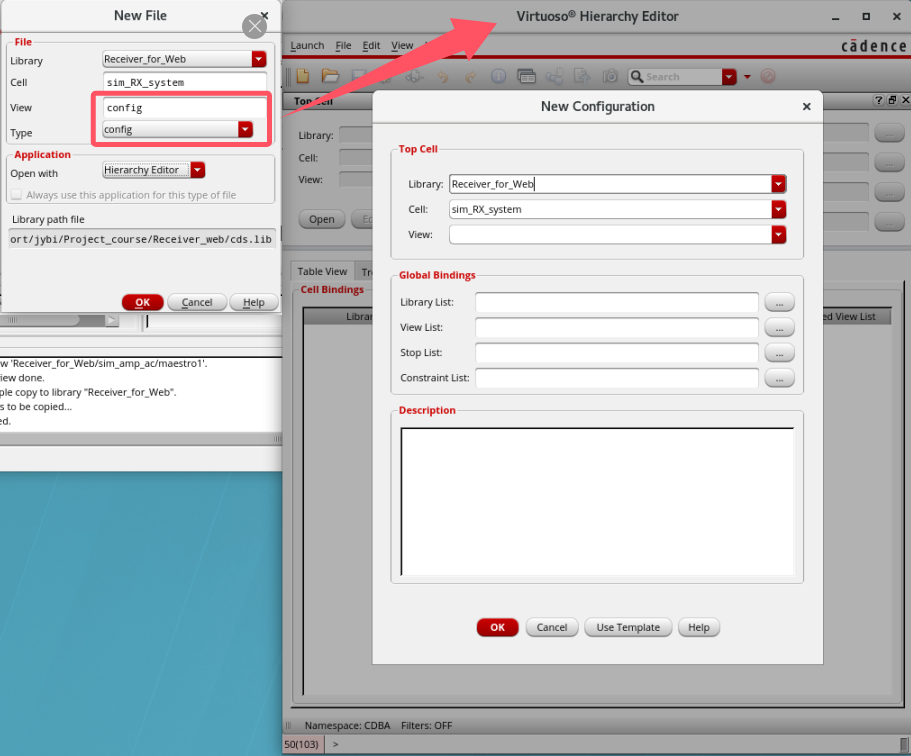

首先需要在 testbench 的 cell 下新建一个 config,可以在 Library Manager 中通过「File -> New -> Cellview」的方法新建,如下图。

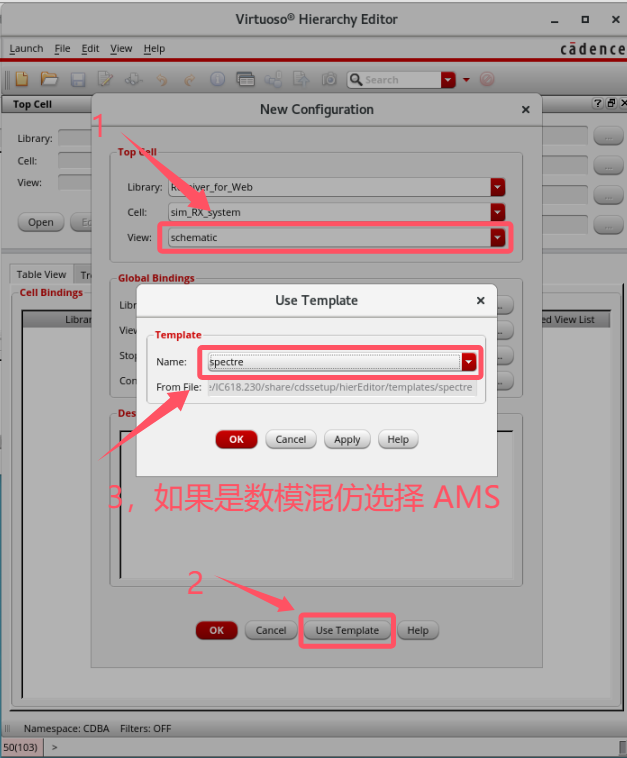

接下来就是对 config 进行一些初始化设置,在弹出窗口中将「View」设置成「schematic」,并选择「Use Template」,随后将「Name」选择为「spectre」,点击 OK 即可。如下图。

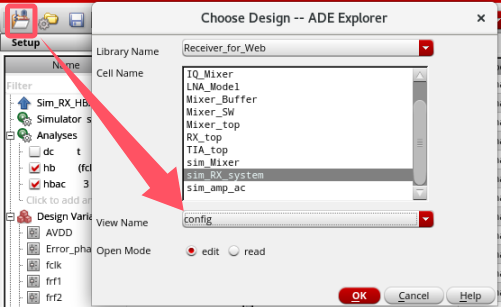

接下来需要在 maestro 中将仿真对应的 Design 选择为 config。具体的方法为在 ADE Explorer 中选择「Setup -> Design」(或者选择上方第一个图标),并在弹出的窗口中选择 tsetench 对应的 Cell View 以及将 View Name 选为 config 即可,如下图。

然后就可以在 config 中切换原理图了。在 config 中需要更改的 Cell 上面右键,选择「Set Cell View」,并选择你想要选择的 View,随后点击一下保存和上传即可,如下图(此处如果将 View 设置为 symbol,则可以在仿真中将这个 Cell 给 Disable 掉)。

此时再在 ADE Explorer 中运行仿真,使用的就是新的原理图了。此时如果点击运行仿真后报错,仿真起不来,那么可以通过更改一下这个 ADE Explorer 的名字解决,具体参考 3.8 节。

3.7.2 开启后仿优化

由于后仿真网表通常非常巨大,因此在运行后仿真时通常速度会非常缓慢。但是其实 Virtuoso 内部是自带了一些后仿真优化功能的,开启这些后仿优化能在一定程度上减少仿真时间,加快进度。

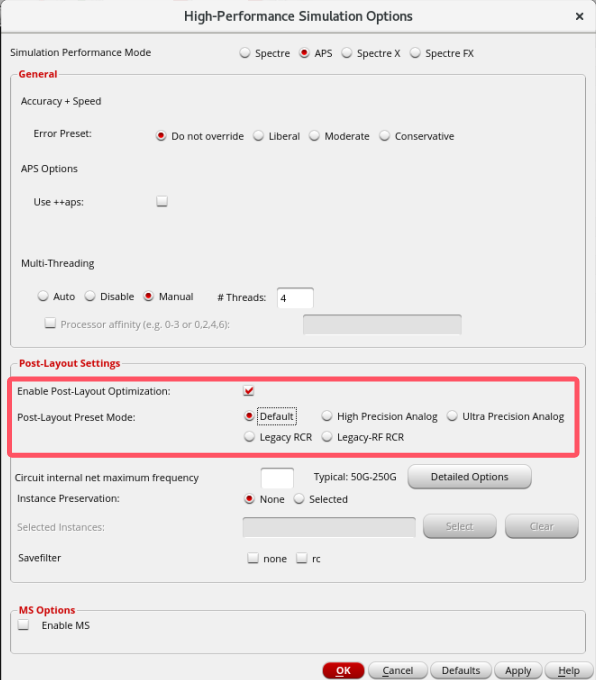

开启后仿真优化需要在 ADE Explorer 名字上右键,选择「High-Performance Simulation」即可打开进程数设置界面(或者「Setup -> High-Performance Simulation」也可打开)。并在打开的界面勾选「Enable Post-Layout Optimization」即可,如下图。

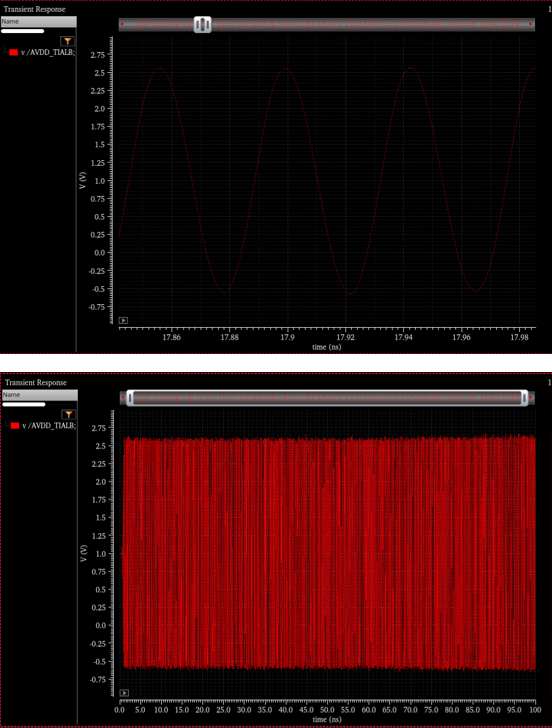

对于后仿真优化的这些 Mode 选项的选择,个人经验是:当大家运行的仿真为时域仿真,并且 testbench 中带有两根及以上的 bonding 电感,那么选择「Legacy-RF RCR」,其余的情况选择「Default」即可。至于为什么某个情况的时域仿真例外,是因为个人试验在这种情况下选择前三种优化方式电路会出现离奇震荡,波形如下图,具体原因不明。

这里挖个坑:后续如果本人有幸接触到 Spectre X 和 Spectre FX 后,会专门出一篇文章讲解一下如何优化后仿真的仿真速度及快速验证后仿真电路功能的问题。

3.8 更改 ADE Explorer 的名字

本章最后来说一下怎么更改 ADE Explorer 的名字,为后续的使用 ADE Assembler 同时运行多个不同的仿真作准备。ADE Explorer 默认生成的名字及其复杂,是由 Library 名 + Cell 名 + 编号组成的,并不方便阅读。同时 ADE Explorer 中并没有提供直接的改名字的选项,因此本人在寻找如何改名字这件事情上也花费了一番功夫,最后找到了一个比较好的方法。

如果想要更改 ADE Explorer 的名字,请大家严格按照我说的做:将鼠标放在 ADE Explorer 的名字上(蓝色的上箭头旁边的文字上),然后,点一下,再点一下。一定要注意不是快速双击,而是温柔的点一下,然后再点一下,如下图。这样做了之后有可能成功的改名,也可能会跳转到 ADE Assembler,大家不要气馁,多试几次就能掌握规律了。

4 同时运行更多仿真——ADE Assembler

第三章讲了一下怎么使用 ADE Explorer 运行仿真,同时配合 Corners 功能也可以在一定程度上实现「收菜」式仿真。但是一个 ADE Explorer 只能运行一种类型的仿真,同时 ADE Explorer 并不能保存仿真记录,一旦点了新的仿真,旧的就会消失。对于接收机这种电路而言,通常需要用不同的仿真配置运行几种不同的仿真才能得到全部的性能参数。而保存历史记录的功能也是非常重要的,它可以作为汇报和 Debug 的一个重要参考。而实现这些功能就需要请出 ADE Assembler 了。

4.1 从 Explorer 转向 Assembler

从 Explorer 转向 Assembler 的方法很简单,只需要点击 ADE Explorer 名字旁边的蓝色上箭头就可以了。点击后界面会变为 ADE Assembler,同时箭头也会变成向下的箭头。再次点击该箭头即可切换回 ADE Explorer。

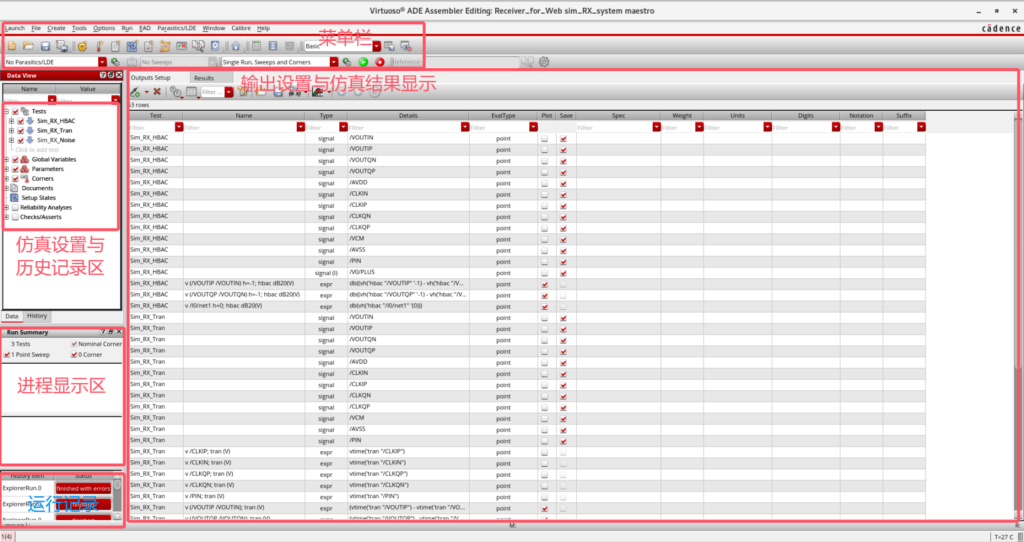

ADE Assembler 的界面相对而言比较复杂,右侧集成了仿真设置、历史记录、进程显示和历史操作显示功能,左侧主要是输出设置和仿真结果显示功能,上面同样是菜单栏。

ADE Assembler 的操作逻辑和 ADE Explorer 类似,可以认为是全局设置和局部设置的区别,因此这里本人并不会进行详细讲解。后面主要会讲一下如何使用 ADE Assembler 进行「收菜」式仿真。

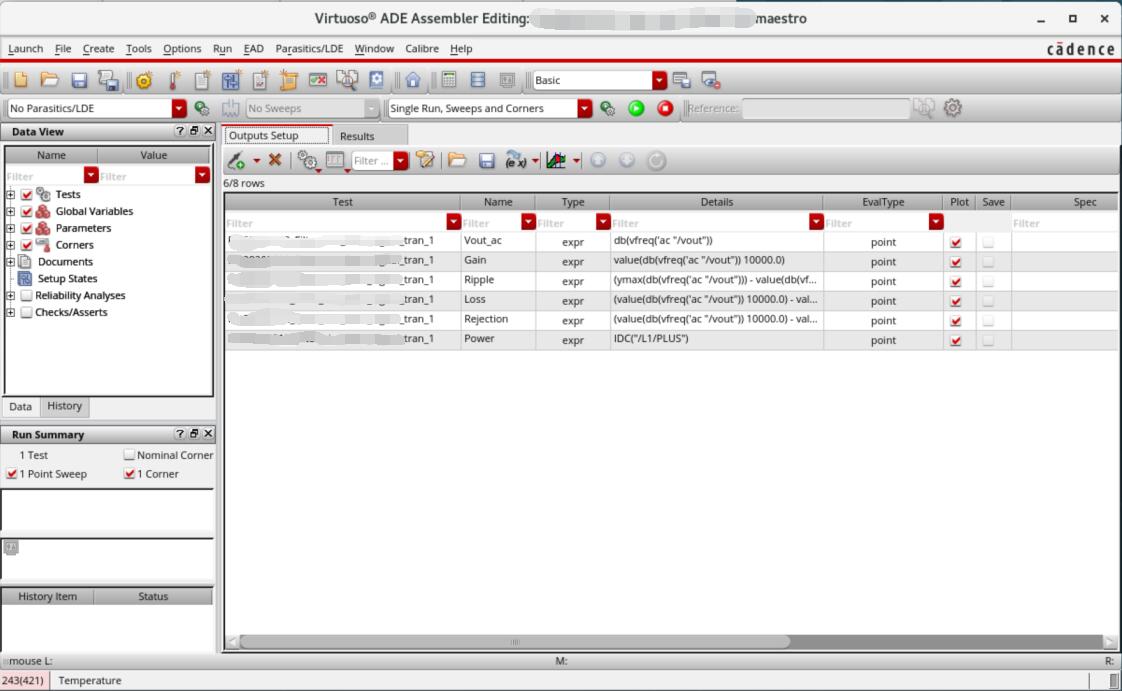

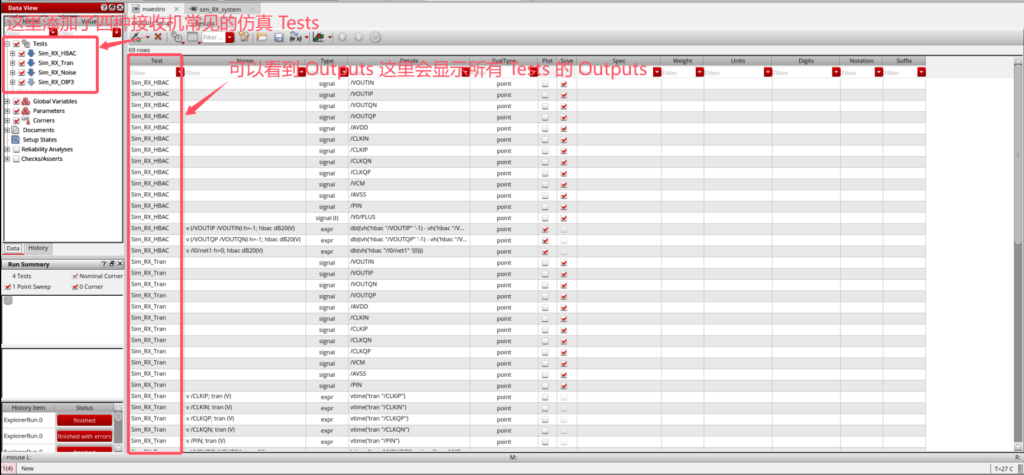

4.2 添加更多 Tests

Assembler 具有极高的自由度,可以在右侧同时添加多个 ADE Explorer,而每个 ADE Explorer 就对应着一个 Test。大家可以将电路仿真涉及到的每种不同的仿真方法都设置为一个仿真 Test,并且每种 Tests 都设置好自己对应的 Outputs,即可实现同时运行多种不同性能参数的仿真,如下图。

此外大家因该可以发现,设置的每个 Test 前面都有一个选择框,如果这个选择框打勾,那么点击运行仿真后会运行这个 Tests;如果不打勾则不会运行。

另外,在每个 Test 上右键或者进入每个 Test 对应的 ADE Explorer 后,就都可以独自设置对应的「Design」、各自的「High-Performance Simulation」以及「Save All」等等设置,这就使得大家可以分别针对每个 Test 对应的 testbench、仿真器配置、优化方式以及存储的节点进行独立的控制,从而大大提升仿真的自由度。

4.3 合理配置 Corners

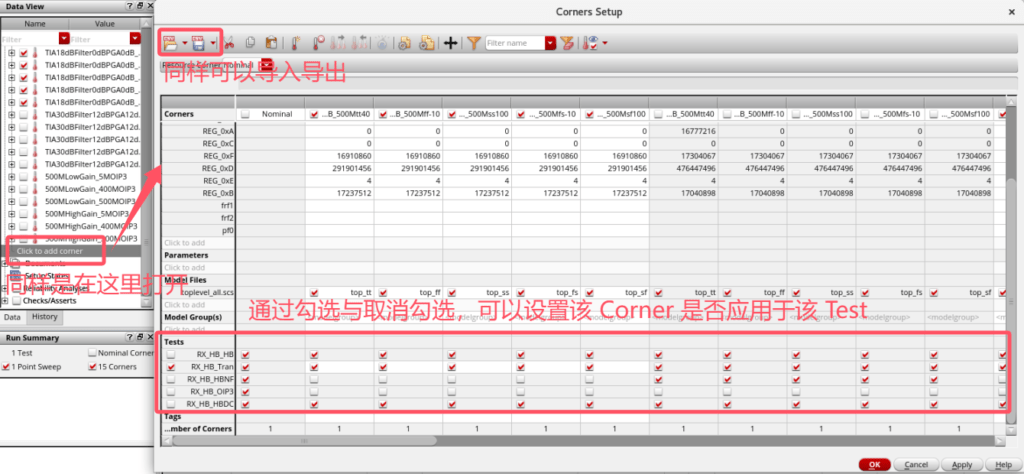

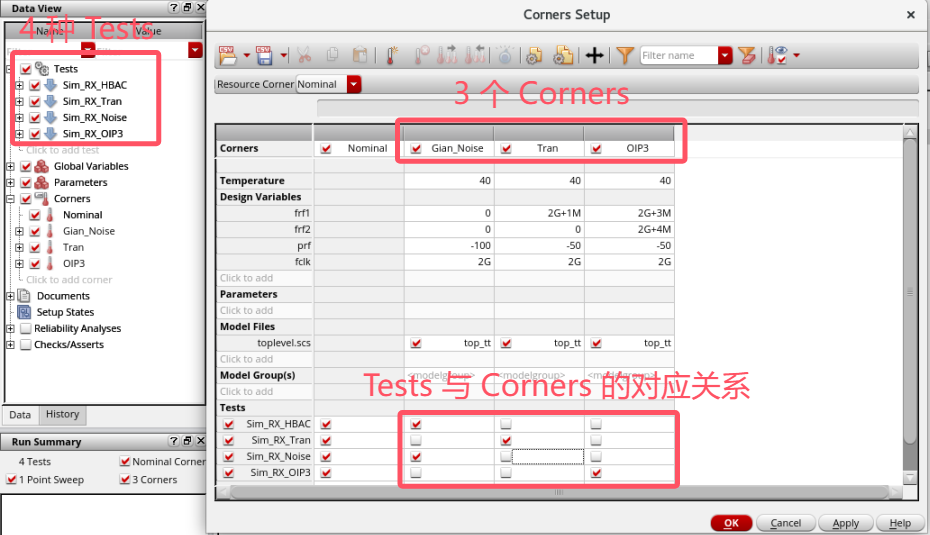

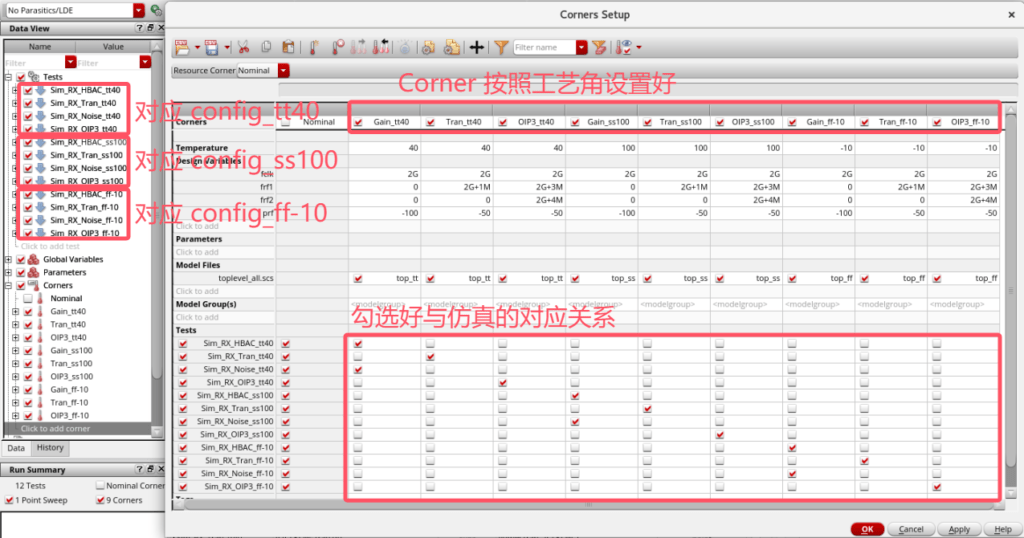

在 ADE Assembler 中,Corners 是实现「收菜」式仿真的核心。ADE Assembler 中能够在全局上对 Corners 进行配置,同时能够管理每个 ADE Explorer 是否启用对应的 Corner。Corners 的具体配置方式与 ADE Explorer 几乎一致,值得提一嘴的只有管理每个 ADE Explorer 是否启用对应的 Corner 的功能。通过勾选或者取消勾选 Corners Setup 中 Tests 选项的勾选框,即可配置该 Test 使用或者不使用该 Corner。

大家在白天工作的时候通过按照前面一节配置好不同的 Tests,在按照这一节配置好各个 Tests 对应的 Corners,然后在下班前点击启动仿真,就可以开启「收菜」式仿真了。经过一段时间的仿真后,各个 ADE Explorer 中设置的 Outputs 已经完完整整的将「菜」端上来了,然后大家只要上班后开始收割就可以了。上午收割、下午配置、晚上服务器仿真、第二天再继续收割,如此循环往复,工作量小的同时还能够快速得到所有的仿真结果,可谓是上班摸鱼之利器。

4.4 多线程运行仿真

ADE Assembler 中同样可以多线程运行仿真,设置方法也在「Options -> Job Setup」中。打开后会发现界面和 ADE Explorer 中的「Job Setup」完全相同。这两者的设置方法也是完全相同的,唯一的区别为 Assembler 控制的是全局设置,因此在这里设置好「Max.Jobs」后,点击开始运行后,一共会并行运行「Max.Jobs」数量的仿真,而不是每个 ADE Explorer 都运行「Max.Jobs」数量的仿真。

这里同样涉及到「Max.Jobs」的合理数值设置问题。假设服务器有 m 个线程,该 Assembler 一共有 k 个 Tests,各个 Test 固定占用的线程数为 $n_1, n_2, …, n_k$,那么推荐的「Max.Jobs」数值设置为 m/max($n_1, n_2, …, n_k$) – 1。此外,由于大概率同一个 ADE Assembler 中的所有 Tests 都对应一个原理图,因此这里强烈建议所有 Tests 都固定使用同样的线程数量。

4.5 保存仿真记录

Assembler 默认最多同时保存 10 个历史仿真记录,对于一个有用的仿真记录,如果不手动保存的话,可能会在仿真的进程中被覆盖掉。因此对于有用的仿真记录需要手动进行保存和锁定,以防止后续刷掉。

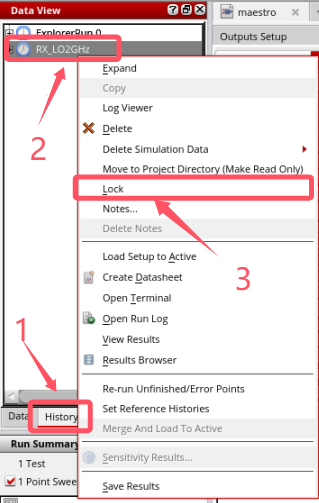

保存前建议先更改一下仿真记录的名字,更改的方式为直接在仿真记录上双击即可。随后在仿真结果上面右键,选择「Lock」即可,如下图。

4.6 一些应用实例

这里本人将描述一些使用过 ADE Assembler 进行快速仿真的配置应用实例,来给大家作为参考。

4.6.1 例 1:需要仿真很多参数的接收机电路

例 1:本文第二章中给出了一个接收机电路。对于该电路,需要仿真它的增益、噪声、线性度、时域输出波形等等参数。该如何配置 ADE Assembler,从而实现对该电路的快速仿真?

解:先理一下此次需要设置几种仿真器配置。增益需要单 tone hb + hbac,噪声需要单 tone hb + hbnoise,线性度需要三 tone hb 仿真即可,时域波形需要 tran 仿真,共有四种。

再看一下此次一共需要几种 Corner。增益和噪声由于不需要射频输入,可以共用一种 Corner 配置;tran 仿真需要一个射频输入,需要一种 corner 配置;而线性度需要两个射频输入,需要一种 Corner。

由此,Assembler 的配置方案已经非常明显了,共需要配置 4 种 Tests,分别用于仿真增益、噪声、线性度和时域;需要配置 3 种 Corners,分别为无射频输入、一个射频输入、两个射频输入。最终配置好的参考 Tests 和 Corners 如下图。

4.6.2 例 2:带工艺角的 nport

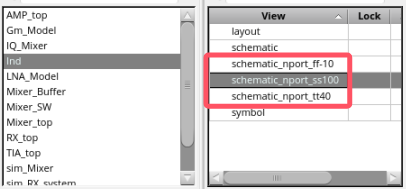

例 2:在使用 EMX 进行 PVT 下的电磁仿真时,会遇到不同的工艺和温度下对应的衬底文件不一致的情况。因此想要运行带有感性无源器件(例如八边形电感)电路的 PVT 仿真,就需要使用 EMX 对应同一个电感分别提取不同的 P 和 T 下的 schematic_nport,随后再用这些不同的 schematic_nport 进行仿真,如下图。这就导致了即使是同一个性能参数,不同的工艺角下也需要使用不同的仿真 schematic,从而大大增加了仿真的复杂性。在这种情况下,怎么才能实现快速的「收菜」式仿真?

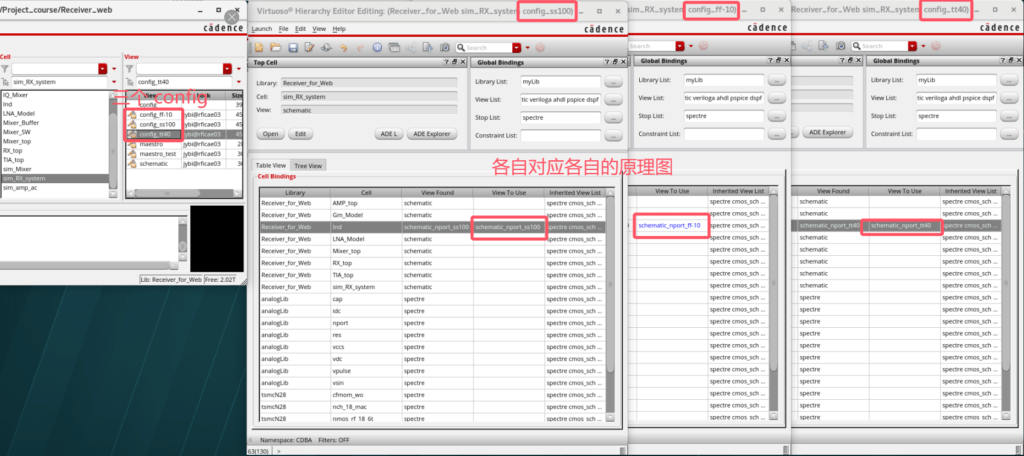

解:注意到每个 Test 对应的「Design」并不需要完全一致,并且 Corners 功能中可以选择每个 Corner 启用的 Test,结合这两个功能即可实现。

首先,我们可以 Copy 出三份 config,分别对应三个工艺角,并在 config 中将该模块的原理图分别设置为三个工艺角对应的 schematic_nport,如下图。

随后,由于 ADE Assembler 具有 Copy Tests 的功能,因此针对同一个仿真(例如增益),我们同样可以按照工艺角要求 Copy 出 3 份出来,并分别以工艺角作为命名后缀,同时三个不同的后缀分别对应三个不同的 config。在 Corsers 设置中也可以如法炮制,对所有的 Corners 按照工艺角要求 copy 三份,并分别以后缀命名,最后确定好工艺角与仿真的对应关系即可。整体 ADE Assembler 配置如下图。

5 结语

仿真验证作为电路设计中的一个最关键的同时也是耗时最长的一步,拥有一个正确高效的仿真验证方法能够加快验证的节奏,同时也能强化验证的系统性和正确性。这里建议大家在原理图参数已经基本确定,并开始进行系统级的仿真和验证后都尽可能使用这种方式进行仿真验证。除了本文中提到的核心之外,maestro 还有很多其他的功能大家可以进行发掘,也欢迎大家进行分享。由于本人入门该专业时间并不长,尚经验不足,如果大家发现本文中有问题和错误,也欢迎在评论区中进行指出。