1 前言

在进行集成电路设计时,通常会遇到需要使用其他公司的 IP 核的情况(例如需要使用 SRAM)。为了保密,这些 IP 核很可能不包含原理图,只包含一个可以应用的版图以及一些必要的用于支持 Cadence 或者 Symopsys 的仿真文件和库文件(例如 Verilog 或者 Verilog-A)等等。 对于这种模块,如何过版图的 LVS 就成了一个需要考虑的问题。

对于这类 IP 核,通常库中还会提供一些用于验证 LVS 的文件,例如网表文件等等。多数情况下这些网表文件是可以被成功导入 Cadence Virtuoso 中去的,但是也存在少量情况下无法导入到 Cadence Virtuoso。这里本人将针对这两种情况,来分别描述一下该如何使用该网表文件验证版图的 LVS。

2 将网表导入 Virtuoso

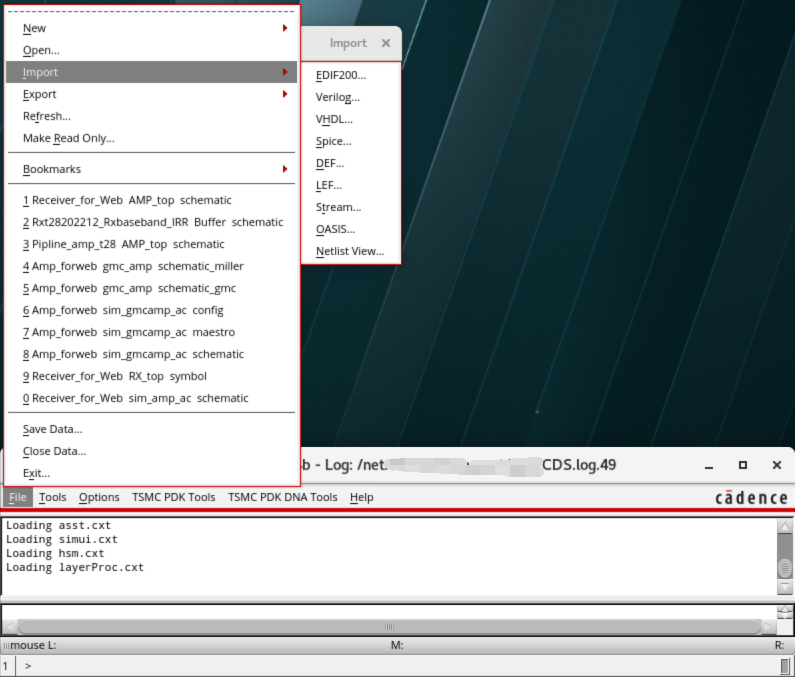

通常情况下,网表文件时可以被导入到 Cadence Virtuoso 中去的,并转化为 schematic。随后就可以使用转换好的 schematic 来验证版图的 LVS 了。这里主要讲一下 Virtuoso 导入网表文件并转换为 schematic 的具体流程。(将只介绍 Spice 和 Verilog 网表文件的导入流程。)

2.1 Spice 网表导入

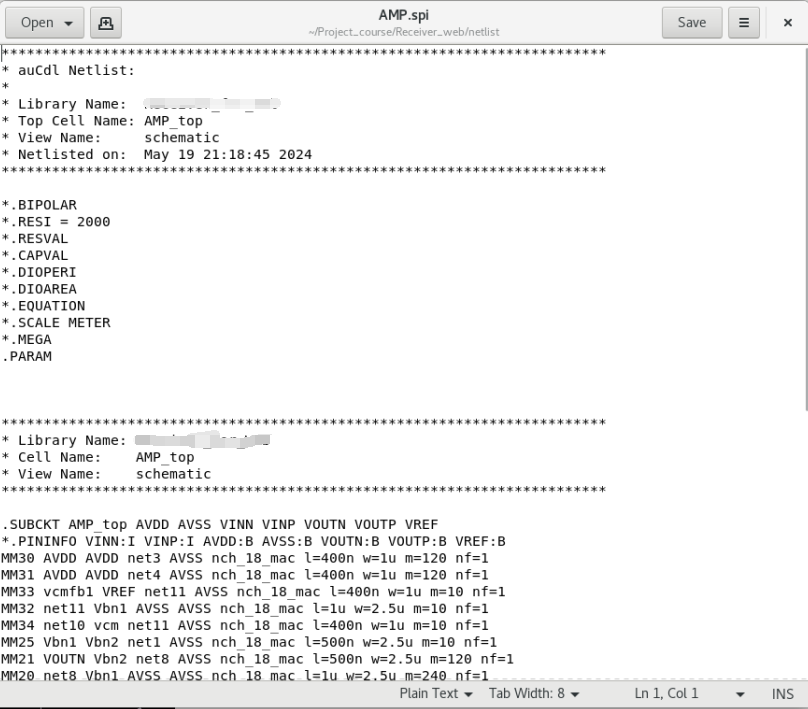

对于 Spice 网表,这里将使用一份已经提前准备好的放大器的 Spice 网表文件进行导入方式演示,如下图:

如上图,打开该网表文件后,可以通过阅读该文件即可得知电路大体的结构组成。其中每条 .SUBSKT 语句即为一个电路 cell,该语句下则列举出了该 cell 调用的其他的 cell 以及相互之间的连接信息。通常 IP 核文件中所带的网表文件也是长这个样子。对于这种网表,具体的导入方式如下:

首先在 Virtuoso 界面中选择 「File-import-spice」,如下图:

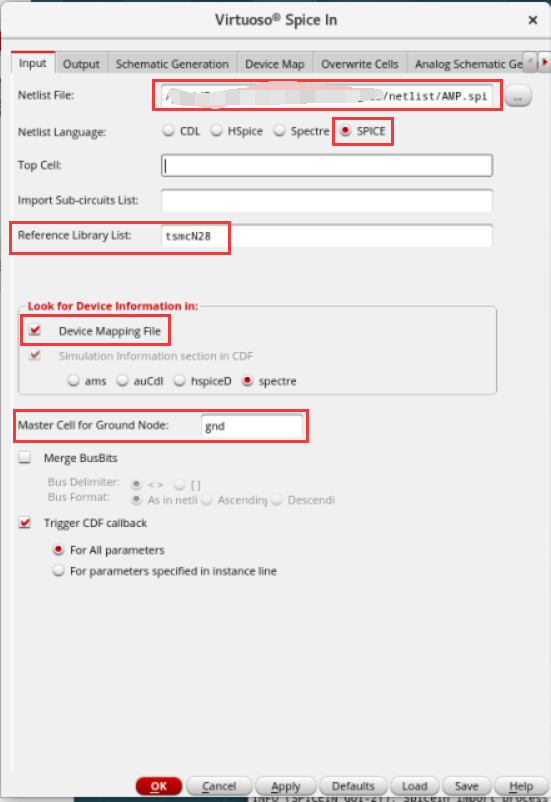

在弹出的界面中设置好网表类型(这个需要根据你拿到的网表来设置,我这边拿到的网表为 SPICE),选择好网表路径,并勾选「Device Mapping File」。同时将导入时参考的工艺库填写在「Refence Library List」中。如果这个网表文件中存在全局地,也应填好全局地的名称,如下图:

接下来就是设置输出库。在「Output」选项卡中填写「Outpet Library」即可,如下图:

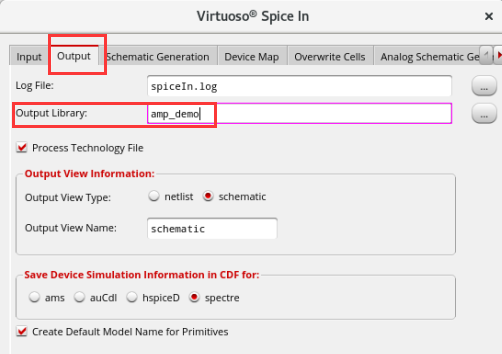

最后一步就是编写 Device Map 了。需要编写这个的原因是因为,通常 Spice 网表中的器件并不一定和工艺库中的器件命名完全一致。例如网表中的 NMOS 可能命名为 nch,而工艺库中的 NMOS 叫做 nmos2v,这样如果强行导入的话,就会报「找不到 nch 这个器件」的错误,因此必须为这个 nch 指配一个对应关系,使 Virtuoso 在导入时能够对应到库里面的器件。

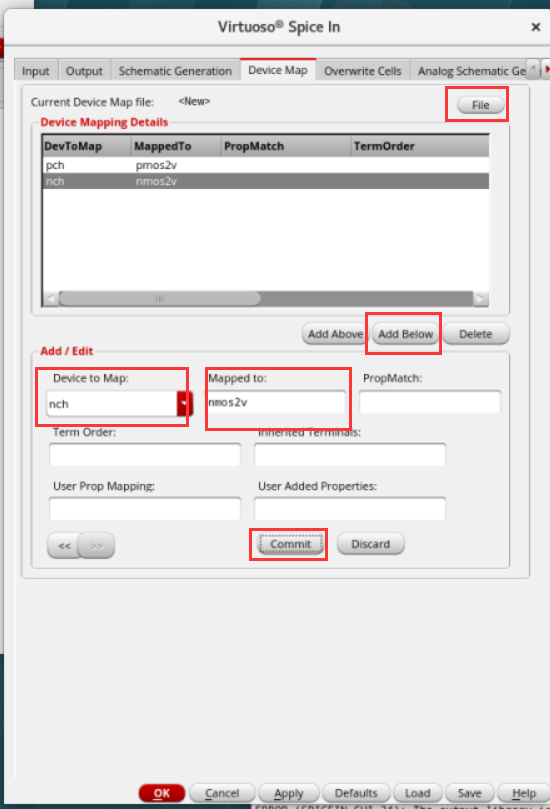

在设置 Device Map 前,需要先明确都需要映射哪些器件。明确好后,在「Device Map」选项卡中选择「File -> New」新建一个 Map File,并选择「Add Below」,随后在下方填写上所需的器件映射关系就可以了,如下图:

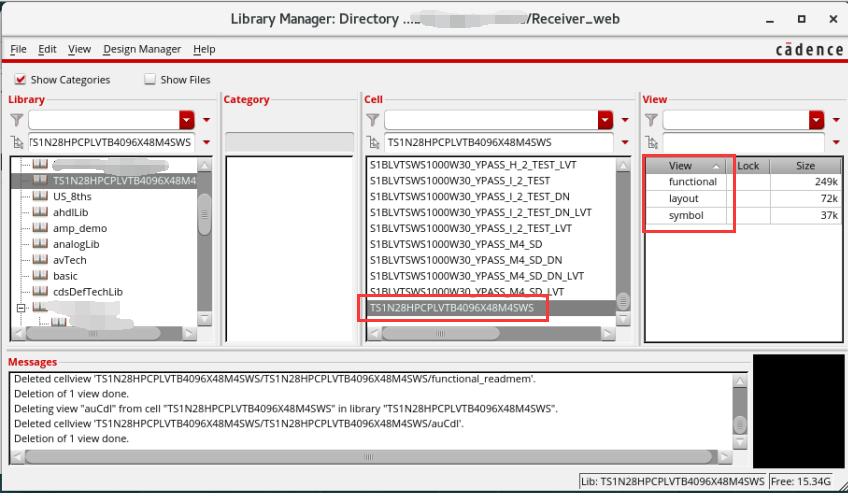

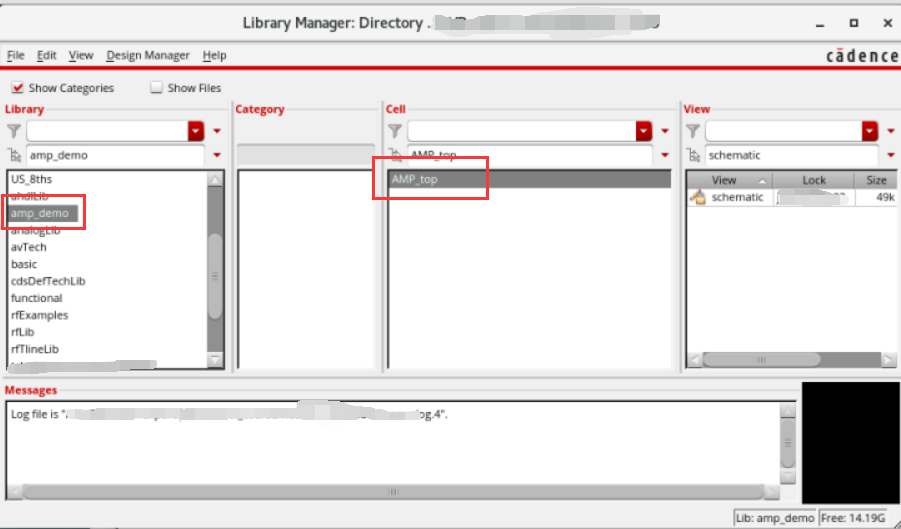

填写完成后,需要再次点击「File -> Save」,将其保存成一个文件。随后点击下面的「OK」就可以导入了。导入完成后,即可在库管理器中找到导入的文件,随后就可以使用这个文件过 LVS 了,如下图:

2.2 Verilog 网表导入

有时候 IP 电路也会提供 Verilog 形式的原理图(这多出现于数字电路相关的 IP 上),这种情况下就可以将 Verilog 导入到 Virtuoso 中,从而生成原理图。这里简述一下具体的导入方式。

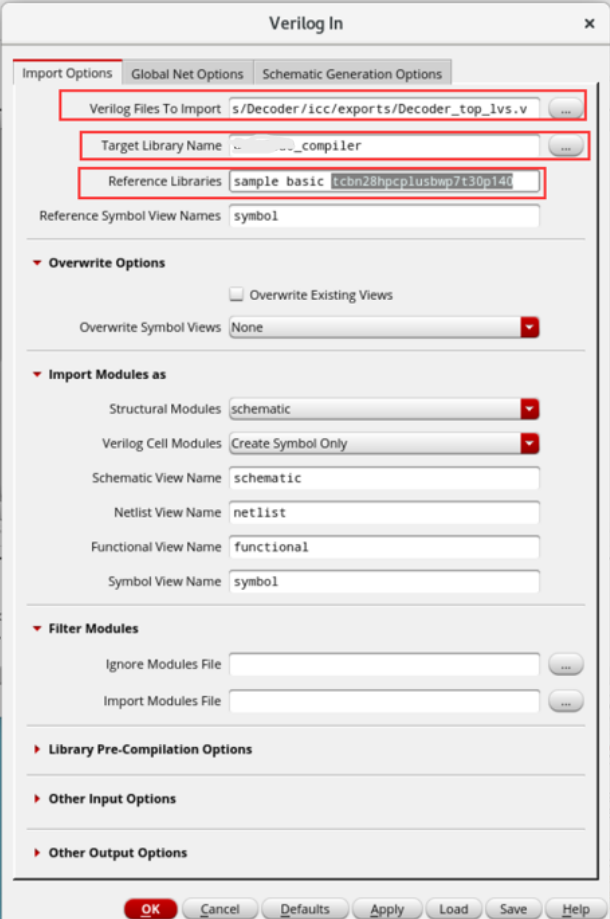

首先在 Virtuoso 中选择「File-import-verilog」,随后会出现如下图所示的窗口:

选择「Import Options」,并在「Verilog Files To Import」中填写需要导入的 Verilog 文件的路径,在「Target Library Name」中要导入的目标库位置,最后在「Reference Libraries」中填写上这个 Verilog 文件对应的数字标准单元库即可。全部填写完成后,点击 OK 就可以完成导入了。

3 无法导入时如何验证 LVS

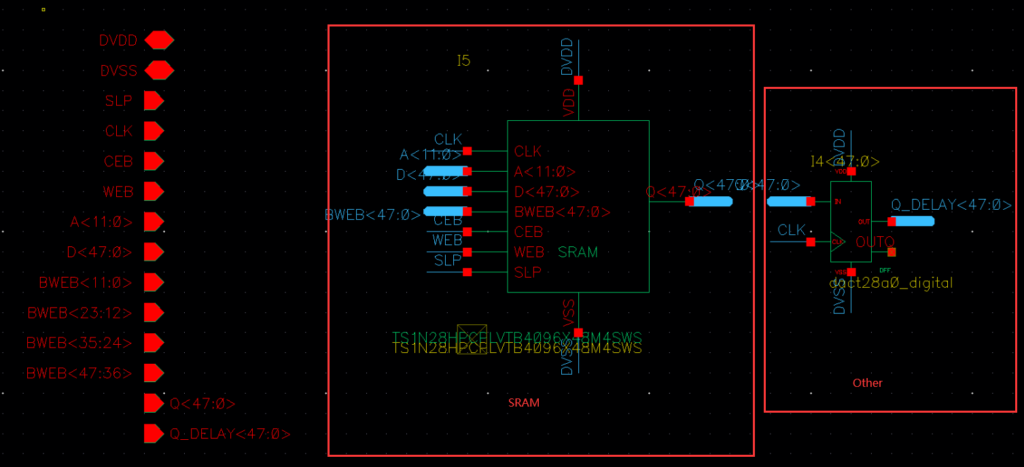

最近本人在进行的一个模拟电路项目中,需要用到 SRAM 电路来存贮一些数据,因此本人也面临了如何过 LVS 的这样一个问题。在 TSMC 的 SRAM 库文件中,提供了一个扩展名为 .spi 的网表文件,用于验证 SRAM 电路的 LVS。本人也曾尝试过将该网表直接导入到 cadence 中,以希望生成一个原理图来用于验证 LVS;但是由于 SRAM 的网表文件中存在一些 TSMC 标准工艺库中并不存在的晶体管器件,因此无法完成原理图的导入,故而作罢,只能被迫去寻找在没有原理图的情况下过掉 LVS 的办法。下面本人将使用一个包含 SRAM 的示例电路来进行过 LVS 方式的演示,如下图:

该电路中包含一个导入好的 SRAM (使用 Stream in 的方式导入 GDS,并使用 SRAM 库中提供的包含电源和地 Pin 的 Verilog 文件成功的建立了一个 Symbol)。对于这样操作下来的 SRAM,它在「Library Manager」中所包含的「View」通常有这些:

其中「functional」是用于仿真的 Verilog 文件,「layout」是导入的版图文件,「symbol」是根据 Verliog 文件生成的 symbol。

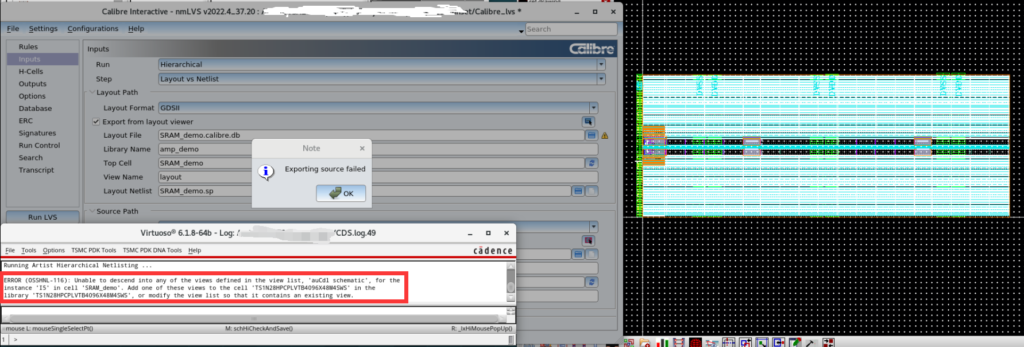

在画好一个包含 SRAM 电路的版图后,需要对这个版图运行 calibre 来验证 LVS。如果按照大家之前的经验直接验证 LVS 时,很可能设置好后 LVS 程序完全无法跑的起来,如下图。这是由于在过 SRAM 这种模块的 LVS 时需要进行一些特殊的设置,下面将对这个问题进行讲解。

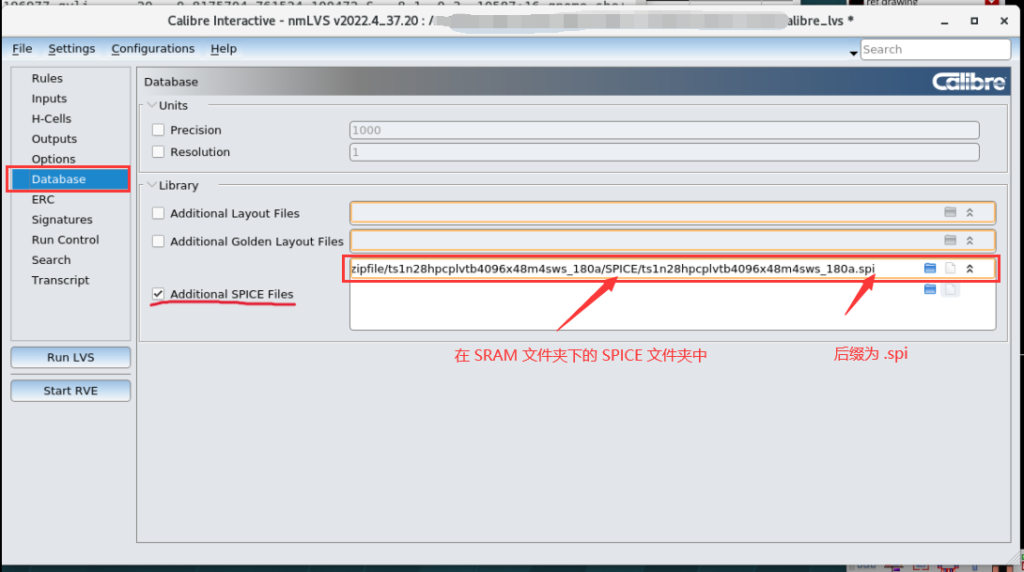

3.1 将 .spi 文件添加进网表数据库中

我们现在的 SRAM 文件还是没有原理图的,因此想要过 LVS,必须把 SRAM 的原理图添加进 calibre 中。但是由于 SRAM 的 SPICE 网表文件中包含特殊器件,因此无法直接将其导入进 Virtuoso 中。好在,calibre 提供了额外附加网表文件的功能,只需在设置 LVS 时选择「Database」选项卡,并在「Library」中勾选「Additional SPICE File」,并在其中选择好 .spi 网表文件所在的路径(通常在 SRAM 文件夹下的 SPICE 文件夹中)即可,如下图:

3.2 添加 .hcell 文件

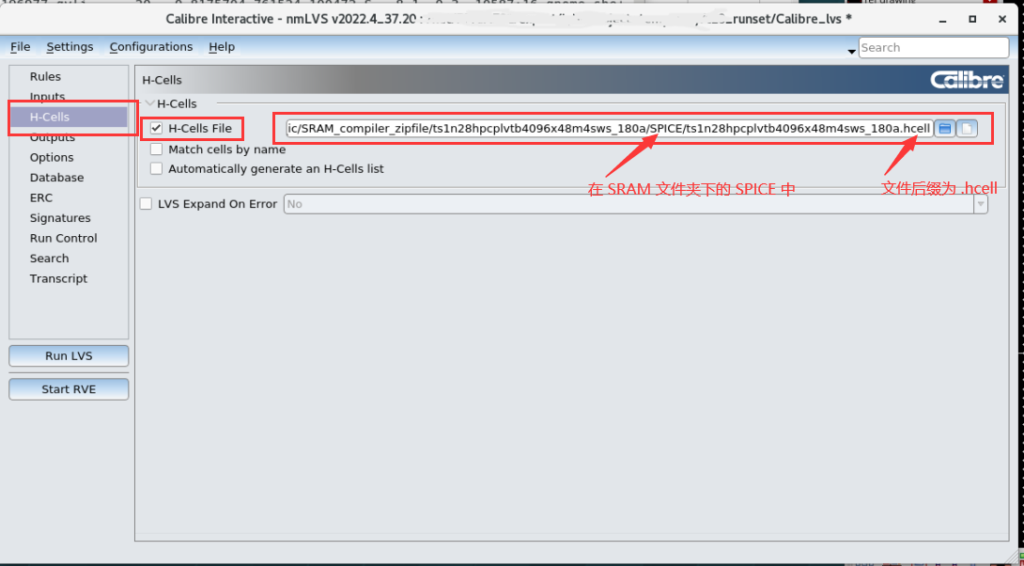

添加好网表文件后,还需要添加一个 H-Cell 文件才可以。H-Cell 文件的用途主要是用来规定版图提取时的层次单元。SRAM 中有一些 TSMC 规定的特殊的子单元,这些单元被记录在 H-Cell 中,如果不添加这个文件可能会导致版图读取出错。H-Cell 的添加方式在 calire 的「H-Cell」选项卡中,勾选「H-Cell File」,并选择相应的文件即可(通常与 SRAM 的 .spi 网表文件在同一目录下),如下图:

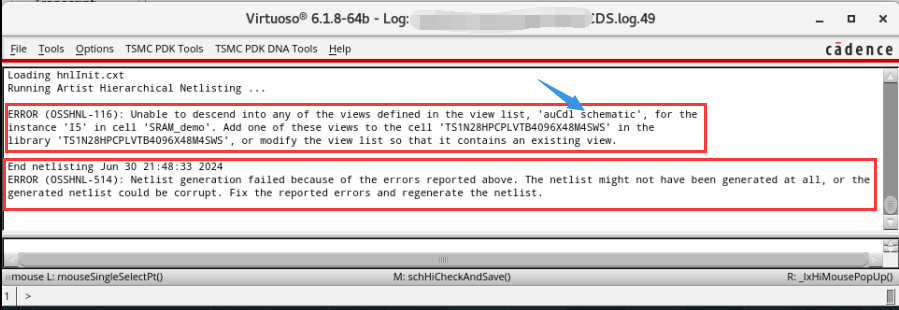

3.3 设置 auCdl View

设置好这两步后,这时我们重新运行 LVS,会发现 LVS 依然跑不起来,并且报错也和之前完全一致,都是「Exporting source failed」。仔细查看 Virtuso 中的报错,会发现它的提示说我们的这个 SRAM 缺少「auCdl」或者「Schematic」,导致无法提取出来原理图,如下图:

但是,由于网表文件无法导入,因此想获得 Schematic 是肯定没戏了,因此只能想想办法,怎么在 auCdl 上作点文章。

auCdl 文件之于 LVS 的作用有点像 Symbol 对我们设计者的作用。它里面会记录这个电路子模块上有哪些端口,同时也会记录一些该子模块的其他特性。caliber 读取了 auCdl 这个文件记录的电路模块端口特性,在抽取网表时就会把这个模块作为一个基本单元去抽取,而不会进一步的深挖这个模块下层的电路连接关系。因此,在过 SRAM 的原理图时,通过给 SRAM 创建一个记录了端口连接关系的 auCdl 文件,再配合上 3.1 节中导入的 .spi 文件,即可实现完成 LVS 的网表文件的生成。

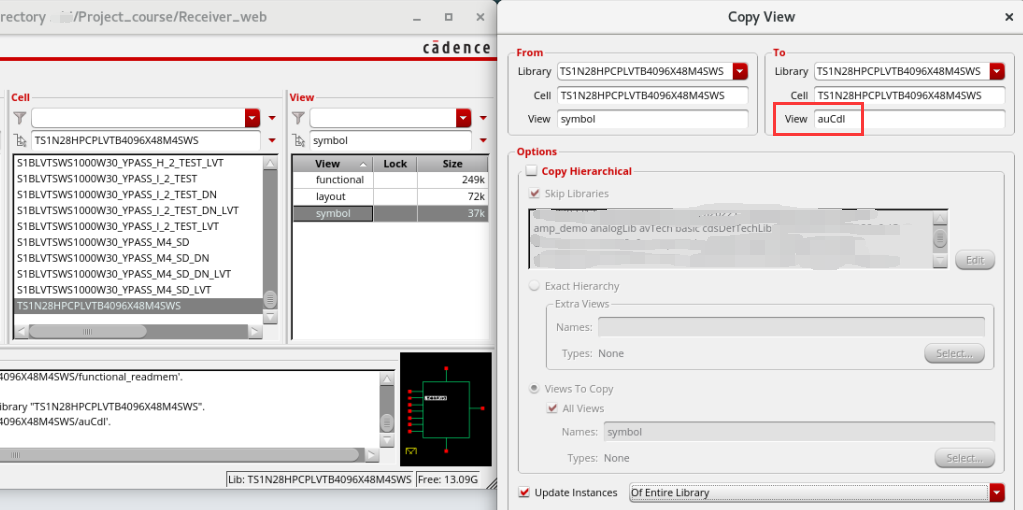

因此,我们首先需要给 SRAM 创建一个 auCdl 文件。对于如何创建这个文件,其实只需要将 SRAM 中的「Symbol」这个 View 复制一下,并改名成 auCdl 就可以了,如下图:

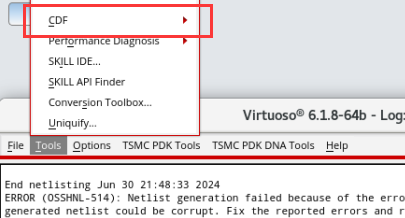

创建好后,接下来就需要对这个文件进行一些设置了。首先在 Virtuoso 中选择「Tool -> CDF -> Edit」,打开 CDF 的编辑界面,如下图:

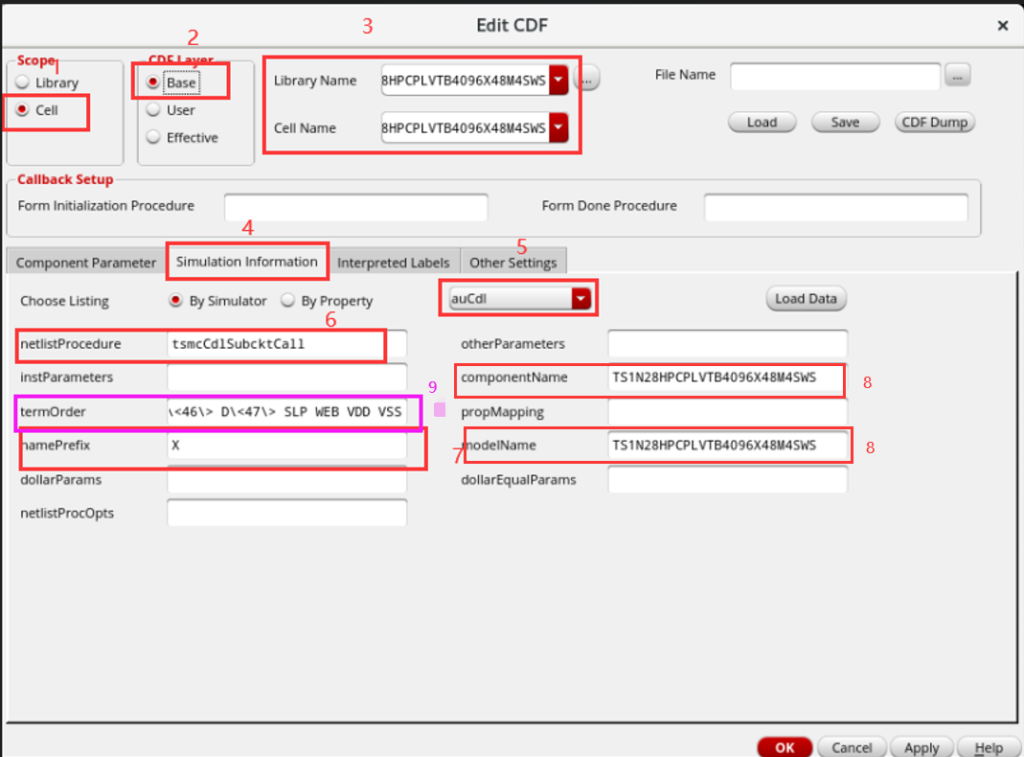

接下来在弹出的界面中,需要依次完成一些设置,如此才能够得到一个可以应用的 auCdl 文件。设置步骤示意图如下图:

第一步,「Scope」处需要选择为「Cell」。第二步,「CDF Layer」处需要选择为「Base」。第三步,需要在「Library」和「Cell Name」处正确的选择 SRAM 对应的库的名字和 Cell View 的名字。第四步,在下面的选项卡中选择「Simulation Information」。第五步,在下拉选项中选择「auCdl」。

第六步,设置「netlistProcedure」为「tsmcCdlSubcktCall」。这个「tsmcCdlSubcktCall」是所有的 TSMC 工艺库中的器件都使用的「netlistProcedure」,不同的工艺库可能会有所不同,具体需要根据自己的工艺库来进行设置。

第七步,设置「namePrefix」为「X」,这个是提取网表是的器件代号,如果设置成 X,那么网表中这个器件的代号就会是 X1, X2, 等。这个建议设置成不常用的字母,以防止字母冲突。

第八步,设置「componentName」与「modelName」。这两个决定了提取出来的网表中,SRAM 子单元的名字。因此,这个必须,一定,要设置成 SRAM 的全称!具体在本人这里就是「TS1N28HPCPLVTB4096X48M4SWS」。这个名称与 SRAM Cell 的名称一致,也与 .spi 网表中的 top 的名称一致。

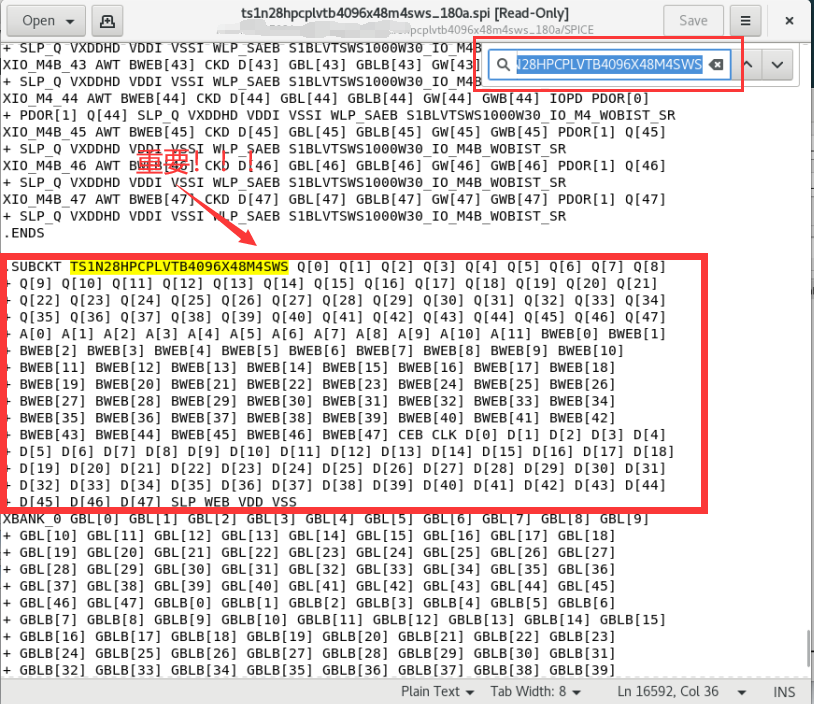

最后一步,也是最重要的一步,就是设置「termOrder」。这一步是最关键的一步。设置这个就是在设置 Calibre 提取出的网表中的 Pin 的排序。要设置这个,需要首先打开 SRAM 对应的 .spi 文件,并在文件中搜索这个 SRAM 的全称(本人这里是 TS1N28HPCPLVTB4096X48M4SWS),如下图:

随后,在.SUBCKT SARM Name之后你就能够得到一份引脚排序,这个引脚排序就是填写「termOrder」的关键信息。

Q[0] Q[1] Q[2] Q[3] Q[4] Q[5] Q[6] Q[7] Q[8]

+ Q[9] Q[10] Q[11] Q[12] Q[13] Q[14] Q[15] Q[16] Q[17] Q[18] Q[19] Q[20] Q[21]

+ Q[22] Q[23] Q[24] Q[25] Q[26] Q[27] Q[28] Q[29] Q[30] Q[31] Q[32] Q[33] Q[34]

+ Q[35] Q[36] Q[37] Q[38] Q[39] Q[40] Q[41] Q[42] Q[43] Q[44] Q[45] Q[46] Q[47]

+ A[0] A[1] A[2] A[3] A[4] A[5] A[6] A[7] A[8] A[9] A[10] A[11] BWEB[0] BWEB[1]

+ BWEB[2] BWEB[3] BWEB[4] BWEB[5] BWEB[6] BWEB[7] BWEB[8] BWEB[9] BWEB[10]

+ BWEB[11] BWEB[12] BWEB[13] BWEB[14] BWEB[15] BWEB[16] BWEB[17] BWEB[18]

+ BWEB[19] BWEB[20] BWEB[21] BWEB[22] BWEB[23] BWEB[24] BWEB[25] BWEB[26]

+ BWEB[27] BWEB[28] BWEB[29] BWEB[30] BWEB[31] BWEB[32] BWEB[33] BWEB[34]

+ BWEB[35] BWEB[36] BWEB[37] BWEB[38] BWEB[39] BWEB[40] BWEB[41] BWEB[42]

+ BWEB[43] BWEB[44] BWEB[45] BWEB[46] BWEB[47] CEB CLK D[0] D[1] D[2] D[3] D[4]

+ D[5] D[6] D[7] D[8] D[9] D[10] D[11] D[12] D[13] D[14] D[15] D[16] D[17] D[18]

+ D[19] D[20] D[21] D[22] D[23] D[24] D[25] D[26] D[27] D[28] D[29] D[30] D[31]

+ D[32] D[33] D[34] D[35] D[36] D[37] D[38] D[39] D[40] D[41] D[42] D[43] D[44]

+ D[45] D[46] D[47] SLP WEB VDD VSS接下来需要做的就是处理这一份引脚排序。首先先将所有的 + 号去除。随后,.spi 文件中的总线是使用方括号 [x] 来表示的,而 Cadence Virtuoso 中是使用尖括号 <x> 来表示的,因此第一步要做的就是将所有的方括号变成尖括号(可以使用记事本的查找替换的功能来处理),如下:

Q<0> Q<1> Q<2> Q<3> Q<4> Q<5> Q<6> Q<7> Q<8> Q<9> Q<10> Q<11> Q<12> Q<13> Q<14> Q<15> Q<16> Q<17> Q<18> Q<19> Q<20> Q<21> Q<22> Q<23> Q<24> Q<25> Q<26> Q<27> Q<28> Q<29> Q<30> Q<31> Q<32> Q<33> Q<34> Q<35> Q<36> Q<37> Q<38> Q<39> Q<40> Q<41> Q<42> Q<43> Q<44> Q<45> Q<46> Q<47> A<0> A<1> A<2> A<3> A<4> A<5> A<6> A<7> A<8> A<9> A<10> A<11> BWEB<0> BWEB<1> BWEB<2> BWEB<3> BWEB<4> BWEB<5> BWEB<6> BWEB<7> BWEB<8> BWEB<9> BWEB<10> BWEB<11> BWEB<12> BWEB<13> BWEB<14> BWEB<15> BWEB<16> BWEB<17> BWEB<18> BWEB<19> BWEB<20> BWEB<21> BWEB<22> BWEB<23> BWEB<24> BWEB<25> BWEB<26> BWEB<27> BWEB<28> BWEB<29> BWEB<30> BWEB<31> BWEB<32> BWEB<33> BWEB<34> BWEB<35> BWEB<36> BWEB<37> BWEB<38> BWEB<39> BWEB<40> BWEB<41> BWEB<42> BWEB<43> BWEB<44> BWEB<45> BWEB<46> BWEB<47> CEB CLK D<0> D<1> D<2> D<3> D<4> D<5> D<6> D<7> D<8> D<9> D<10> D<11> D<12> D<13> D<14> D<15> D<16> D<17> D<18> D<19> D<20> D<21> D<22> D<23> D<24> D<25> D<26> D<27> D<28> D<29> D<30> D<31> D<32> D<33> D<34> D<35> D<36> D<37> D<38> D<39> D<40> D<41> D<42> D<43> D<44> D<45> D<46> D<47> SLP WEB VDD VSS这一步处理完毕后,由于 CDF 设置无法直接识别尖括号 <x>,为了将它填写进 CDF 设置中,还需要将所有的尖括号修改为转义字符的形式,具体的方法是将 < 替换为 \<;将 > 替换为 \>,如下:

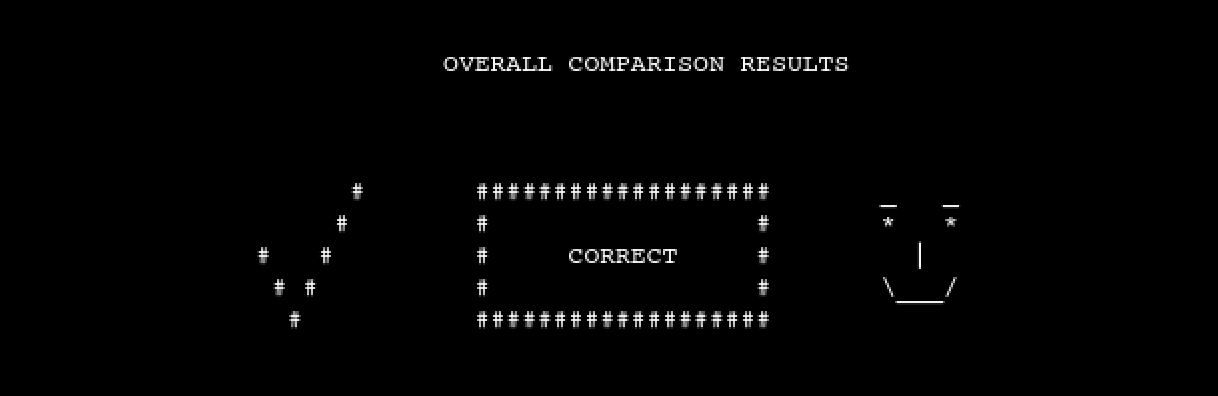

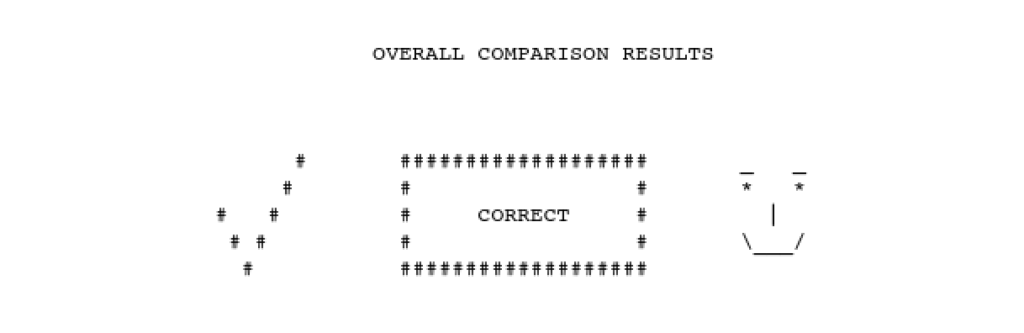

Q\<0\> Q\<1\> Q\<2\> Q\<3\> Q\<4\> Q\<5\> Q\<6\> Q\<7\> Q\<8\> Q\<9\> Q\<10\> Q\<11\> Q\<12\> Q\<13\> Q\<14\> Q\<15\> Q\<16\> Q\<17\> Q\<18\> Q\<19\> Q\<20\> Q\<21\> Q\<22\> Q\<23\> Q\<24\> Q\<25\> Q\<26\> Q\<27\> Q\<28\> Q\<29\> Q\<30\> Q\<31\> Q\<32\> Q\<33\> Q\<34\> Q\<35\> Q\<36\> Q\<37\> Q\<38\> Q\<39\> Q\<40\> Q\<41\> Q\<42\> Q\<43\> Q\<44\> Q\<45\> Q\<46\> Q\<47\> A\<0\> A\<1\> A\<2\> A\<3\> A\<4\> A\<5\> A\<6\> A\<7\> A\<8\> A\<9\> A\<10\> A\<11\> BWEB\<0\> BWEB\<1\> BWEB\<2\> BWEB\<3\> BWEB\<4\> BWEB\<5\> BWEB\<6\> BWEB\<7\> BWEB\<8\> BWEB\<9\> BWEB\<10\> BWEB\<11\> BWEB\<12\> BWEB\<13\> BWEB\<14\> BWEB\<15\> BWEB\<16\> BWEB\<17\> BWEB\<18\> BWEB\<19\> BWEB\<20\> BWEB\<21\> BWEB\<22\> BWEB\<23\> BWEB\<24\> BWEB\<25\> BWEB\<26\> BWEB\<27\> BWEB\<28\> BWEB\<29\> BWEB\<30\> BWEB\<31\> BWEB\<32\> BWEB\<33\> BWEB\<34\> BWEB\<35\> BWEB\<36\> BWEB\<37\> BWEB\<38\> BWEB\<39\> BWEB\<40\> BWEB\<41\> BWEB\<42\> BWEB\<43\> BWEB\<44\> BWEB\<45\> BWEB\<46\> BWEB\<47\> CEB CLK D\<0\> D\<1\> D\<2\> D\<3\> D\<4\> D\<5\> D\<6\> D\<7\> D\<8\> D\<9\> D\<10\> D\<11\> D\<12\> D\<13\> D\<14\> D\<15\> D\<16\> D\<17\> D\<18\> D\<19\> D\<20\> D\<21\> D\<22\> D\<23\> D\<24\> D\<25\> D\<26\> D\<27\> D\<28\> D\<29\> D\<30\> D\<31\> D\<32\> D\<33\> D\<34\> D\<35\> D\<36\> D\<37\> D\<38\> D\<39\> D\<40\> D\<41\> D\<42\> D\<43\> D\<44\> D\<45\> D\<46\> D\<47\> SLP WEB VDD VSS随后,就可以将上面这样一份列表粘贴到「termOrder」中去了。至此,CDF 设置完成。设置完成 CDF 后,点击 OK 进行保存,随后就可以愉快的跑 LVS 了:

后记

对于做模拟的本人来说,为了跑一个 SRAM 的 LVS,实在是不容易。在遇到这个问题时着实折腾了我们许久,幸好最终找到了这样一个可行的解决方案。对于这种数模混合的电路,在设计时确实充满了各种问题和挑战,但是很多时候却又很难去获得具体的解决方案。希望能早日有更多的人愿意分享自己的经验吧。

致谢

感谢 Bcaritas 对本文内容上和方法寻找上的协助,祝你在模拟电路的道路上能够走的更深更远。

您好,我也在做 SRAM Compiler 生成的 SRAM 的 LVS,我尝试一种简单方法,您看是否可行?看到的话,请您回复、讨论

先前步骤与您相同,在步骤3.3,LVS的 input 选项卡中 –> Spice Files一栏 –> 选择 xxx. spi 文件 –> 运行 LVS –> 正确,笑脸

你好,我看我们这边的区别是你这边只要在 LVS 的 input 的选项上加上 .spi 文件就可以运行了。不知你用的 SRAM 是 tsmc 的吗?进行 LVS 时是否是对「SRAM 自身的版图」过 LVS,而不是对「包含有 SRAM 电路和版图的更高一层级电路」过 LVS?如果只是对「SRAM 自身的版图」过 LVS 的话,我这边像你这么操作也是能过的。我这篇文章主要是针对「包含有 SRAM 电路和版图的更高一层级电路」过 LVS 这种情况。

上一个问题,您说的是对的。我是用Tsmc28的工艺。请问一下,调用MC生成的SRAM,在schematic中连接成多模块电路,画版图时候,因为SRAM的版图只有label没有pin,大电路的pin与SRAM的版图没有连接关系,不能自动飞pin到SRAM版图上,需要手动一个个连接,且不知道对不对,请问您是如何画这种带SRAM的多模块电路版图?感谢🙏

是的,我这边也是只能手动一个一个连接,默认的 SRAM 版图只有 label,没有 pin。或许你可以试一下改一下 SRAM 版图,可以在版图菜单中使用「Tools」->「Create Pins form Labels」来生成 pin,这样更高层调用因该就能自动飞线连接了。

请问,您有没有尝试过LVS BOX ,将【 sram】 的版图屏蔽,LVS 只检查 【sram】与【其他电路】的连接关系,把【sram】版图当作黑盒子。我尝试用BOX,也可以过 大电路 的LVS,而无需改【网表】等操作。请教您的看法

我这个尝试过的,这样虽然能满足过 SRAM LVS 的需求,但是这样有一个很大的问题,就是 SRAM 被 BOX 掉了。如你所说,LVS 只检查 SRAM 与「其他电路」的连接关系,并不检查 SRAM 内部的内容。这样在大多数情况下是没问题的,但是假设在版图绘制阶段,不小心把一段走线移动到 SRAM 上了,或者是连接 SRAM 电源和地的时候不小心连接错了,对于这种错误就可能查不来。我们一开始也考虑过这样的方案,但是这种方案最大的问题就是不保险,因此最后还是选择了使用网表检查,这样能确保 SRAM 内部电路正确,不会因小小失误而造成严重后果。