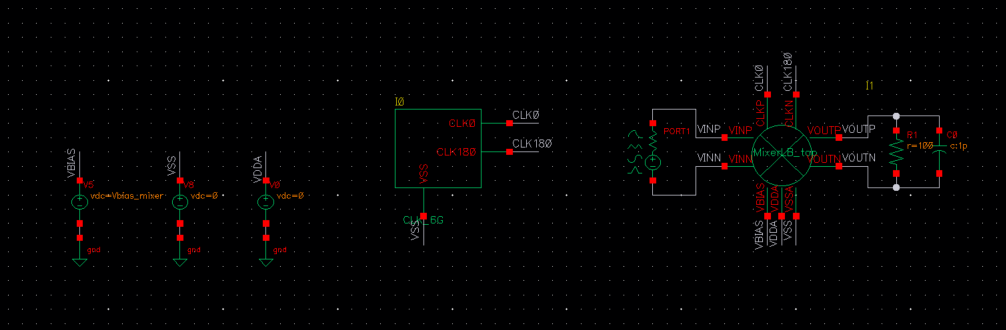

在进行集成电路设计时,通常会遇到需要使用其他公司的 IP 核的情况(例如需要使用 SRAM)。为了保密,这些 IP 核很可能不包含原理图,只包含一个可以应用的版图以及一些必要的用于支持 Cadence 或者 Symopsys 的仿真文件和库文件(例如 Verilog 或者 Verilog-A)等等。 对于这种模块,如何过版图的 LVS 就成了一个需要考虑的问题。

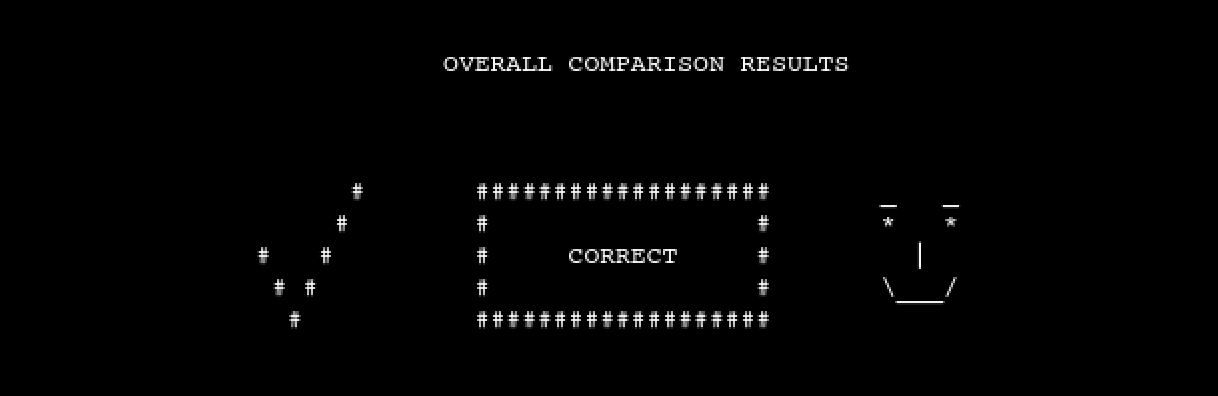

对于这类 IP 核,通常库中还会提供一些用于验证 LVS 的文件,例如网表文件等等。多数情况下这些网表文件是可以被成功导入 Cadence Virtuoso 中去的,但是也存在少量情况下无法导入到 Cadence Virtuoso。这里本人将针对这两种情况,来分别描述一下该如何使用该网表文件验证版图的 LVS。