前言

之前的一篇文章中简单的介绍了一下使用 Cadence IC617 中的蒙特卡洛仿真器来仿真单端运放的失调电压的方法,同时还放出了那个示例运放的失调电压仿真结果。但是从那个仿真的结果中可以看出,这个运放的 3σ 失调达到了 12.66 mV。对于很多应用(例如温度传感器等)来说,这是一个非常大的失调电压值,在很多情况下是不可接受的。而使用斩波调制的方式是降低失调电压的一种非常好的方法。因此这篇文章将简要的介绍一下斩波调制技术,以及如何仿真斩波运放的等效输入失调电压。

1. 斩波调制技术

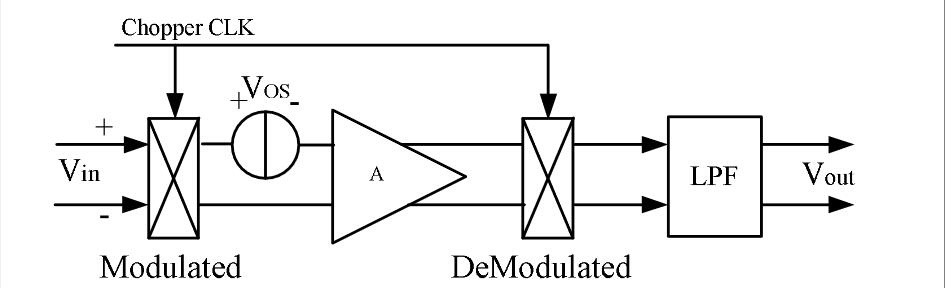

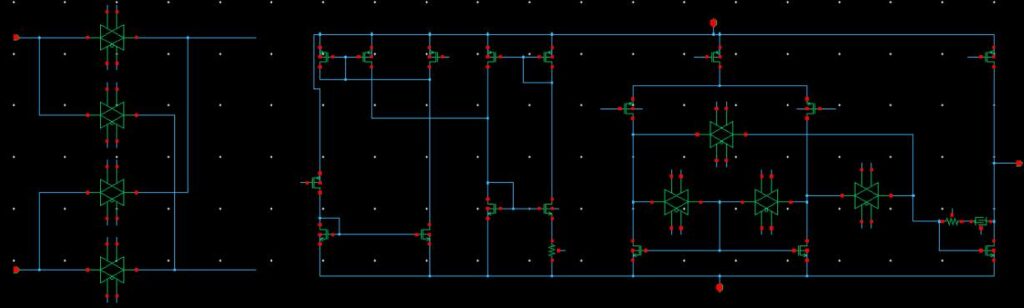

斩波技术 (Chopper Technique)是采用调制和解调原理,将低频噪声和失调搬移到高频部分,进而使用低通滤波滤除的一种技术手段。对于一个全差动的运放来说,斩波放大器的工作原理可以用下图表示[1]:

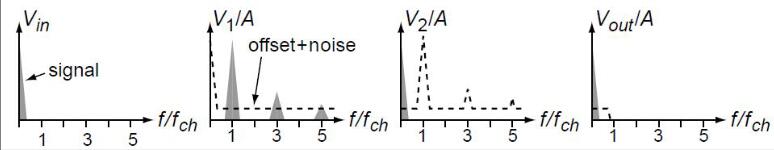

输入信号在经过第一个斩波开关后被搬移到高频,而经过第二个斩波开关后又被搬移回低频。而低频的失调以及 1/f 噪声,只经过了一个斩波开关,因此在斩波调制后被搬移到高频,进而可以被后面的低通滤波器除去。相关的信号频谱如下图所示:

通过这个频谱图可以看出,斩波调制技术可以将运放的噪声和失调信号搬移到高频,进而可以使用后面的低通滤波器除去,达到降低运放的失调和噪声的结果。

2. 带斩波的单端运放原理图

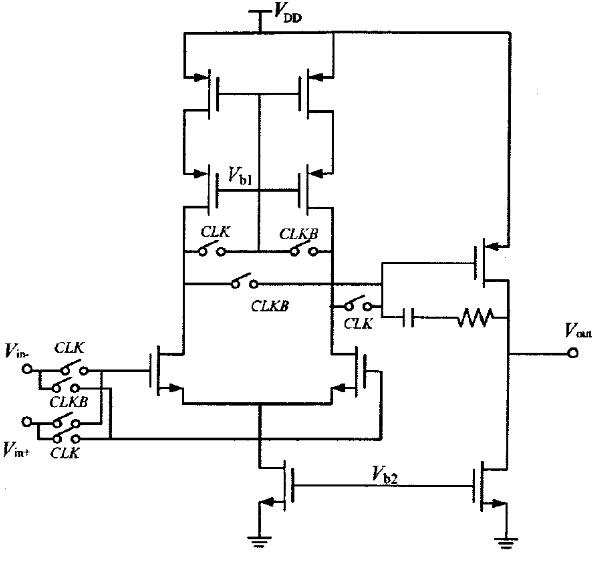

如果想要给一个单端运放加上斩波,需要在输入端加入开关进行调制,同时第一级和第二级也加入开关完成解调,如下图[2]:

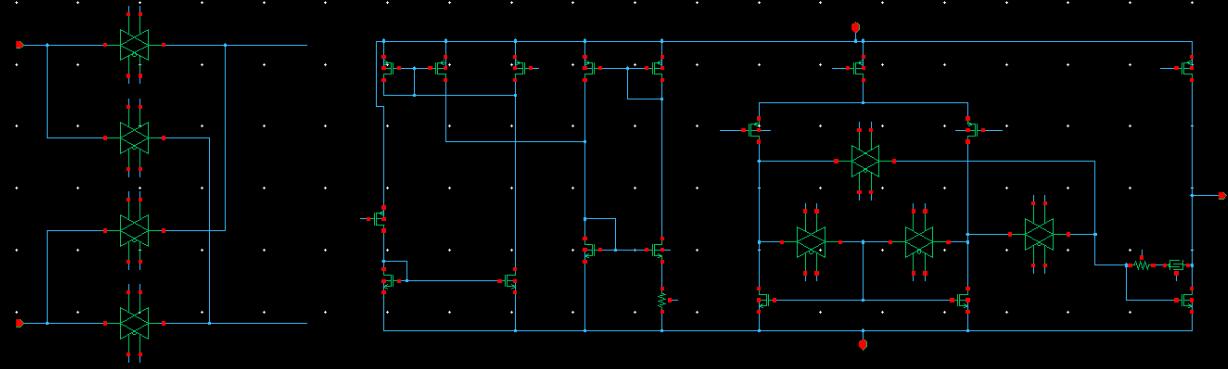

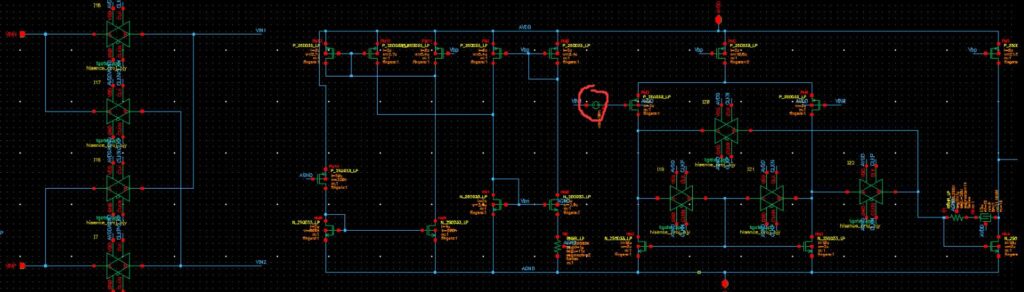

本人使用了 CMOS 传输门来做开关,MOS 的栅长就取最小值,栅宽取几个微米即可。最终用来仿真的斩波运放的原理图如下图:

3. 斩波运放的失调电压仿真方法

3.1 仿真前的准备

在进行斩波运放的失调电压仿真前,推荐先使用 Cadence 的 noise 仿真器仿真一下不带斩波的运放的噪声特性。进行完噪声特性仿真后,可以获得运放的 1/f 噪声的拐点频率。通过该拐点频率进而可以确定斩波时钟的频率。

3.2 仿真电路的搭建

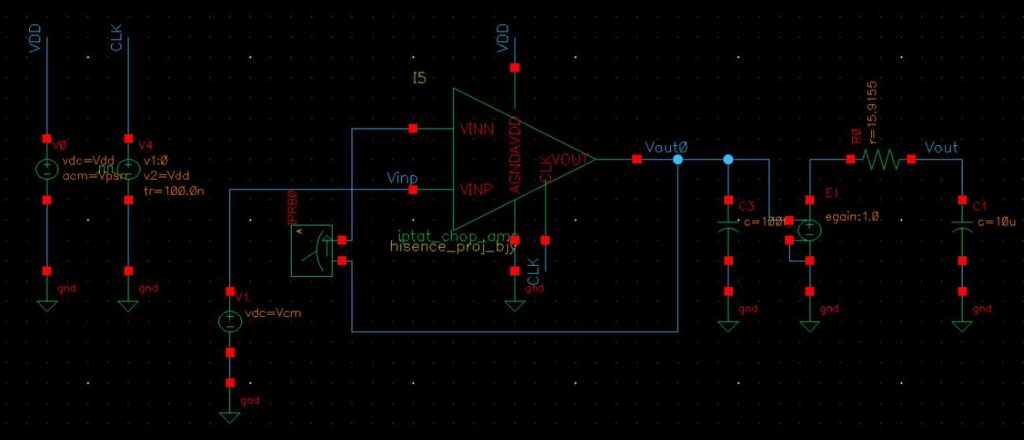

仿真斩波运放的失调电压时,仿真电路的搭建也是一个很重要的工作。本人最终搭建的仿真电路如下图所示:

这里简要的说明一下关于这个仿真电路的几个关键问题:

- 斩波电路需要配合低通滤波器才能正常的工作,将失调消除。为了仿真方便这个滤波器可以使用一个一阶的 RC 低通滤波器。而如果直接将一个 1 阶 RC 网络组成的低通滤波器接在运放的输出端,会严重的影响运放的直流增益(由于接之前第二级的输出电阻为 MOS 的 $r_o$ ,为高阻,但是接之后就成了 RC 的 R,变成低阻了)。因此,必须经过一个 VCVS,再接入 RC 网络。这样 RC 网络的接入对原运放的工作点无任何影响,同时还可以起到滤波消失调的效果。

- 对于 RC 网络参数的选取,个人认为总体的思路为要使得 RC 的 3 dB 带宽足够的小,但是不能过于小。足够的小是为了保证 RC 滤波器能够尽可能得将失调电压滤除掉;但是如果 RC 网络的 3 dB 带宽设置的太小,在进行仿真时就会发现,需要经过相当长的时间后输出电压才能收敛到消除失调后的电压,这样会造成为了追求收敛而被迫增长仿真时间,最终导致仿真速度奇慢无比。

3.3 选取 RC 网络的 3 dB 带宽值

本文上一节中已经说明了 RC 网络值选取的重要性,这里给大家提供一种选取该值的方法,供大家参考:

(1). 首先搭建好仿真电路,然后人为的在斩波运放的某一个输入端引入一个一定大小的失调电压(本文设置的是 10 mV),如下图:

(2). 根据你的斩波时钟的频率取一个较为正常的仿真时间(本文所用的斩波频率为 100 k,仿真时间取 1 ms),使用之前搭建的仿真电路进行 tran 仿真,同时将运放的输出端与 RC 网络的输出端的电压波形添加到 ADE L 的输出中。

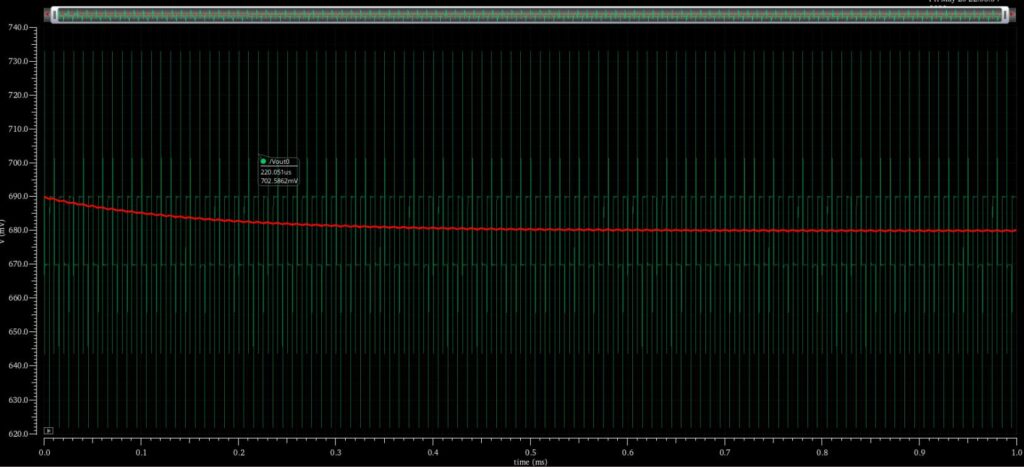

(3). 观察仿真波形的形状,如果最后的 RC 网络的输出收敛的非常快,同时收敛之后输出端的波动还比较大,则 RC 网络的 3 dB 带宽取得太大了,可以适当的缩小;如果 RC 网络的输出收敛的很慢甚至几乎不收敛,这说明 RC 网络的 3 dB 带宽取得太小了,需要增大。本文在取一个适当的带宽后,RC 网络输出的 tran 仿真结果如下图:

(4). 去掉之前人工加入的失调。

3.4 进行蒙特卡洛仿真

在进行蒙特卡洛仿真时,如果还像之前的那一篇文章那样设置仿真输出的话,是不能够正确的获得失调电压的概率分布曲线的。为了正确的获得概率分布曲线,可以使用 Cadence 中的 value 函数,来获取某一个时刻的电压值。这时可以把输出设置为:value((VT(“/Vout”) – VT(“/Vinp”)) time),这样就可以正确的输出我们想要的概率分布曲线了。

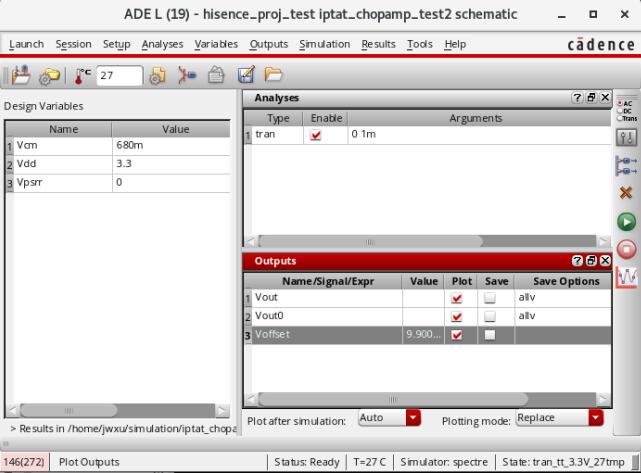

至于这个 time,需要根据读者自己的仿真时间去进行设置。本人设置的仿真时间为 1 ms,因此这个时间设置为 0.0009975,即 0.9975 ms(这是一个在仿真最后且刚好处于两次斩波之间的时刻)。设置完成后的 ADE L的仿真界面如下图:

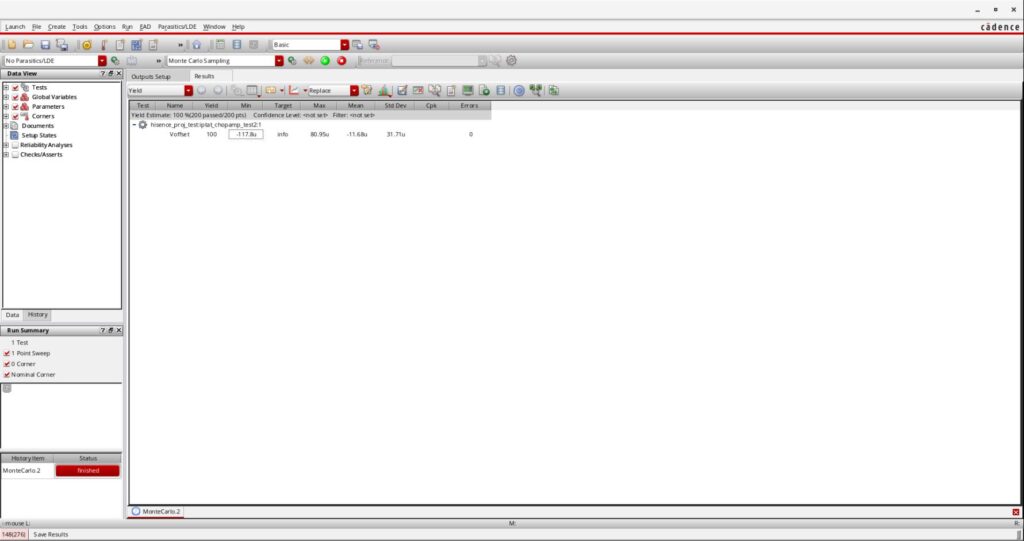

随后,就可以打开 ADE XL 仿真器,进行蒙特卡洛仿真了。由于这一次蒙特卡洛要跑很多次的 tran 仿真,因此仿真速度会比较慢,大家耐心等待即可。仿真完成后的 ADE XL 如下图所示:

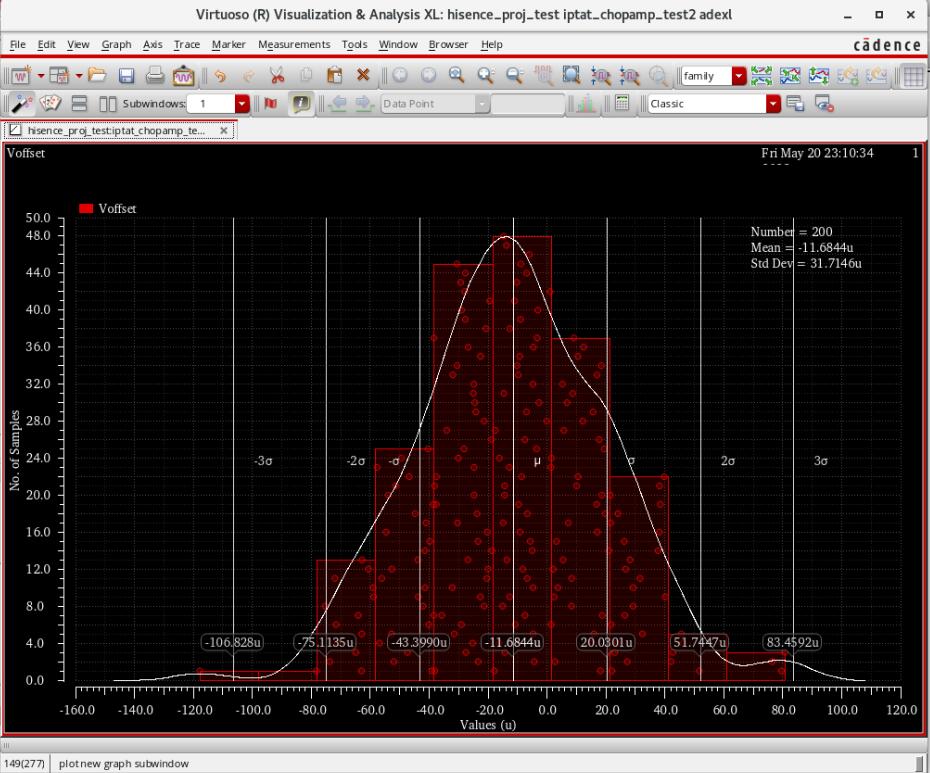

这时就可以得到我们想要的概率分布曲线图了:

通过仿真可以看出,将原来的运放加上一个斩波后,3σ 失调变为了 -106.8 uV。通过与之前的一篇不加斩波的运放的失调电压仿真结果对比,可以看出添加斩波后该运放的失调电压比填加斩波前低了 100 多倍。由此可以看出斩波调制对降低运放的失调电压的效果是十分显著的。

您写的非常好,令我受益匪浅!

请教一个问题:最后提到取0.9775ms时刻的VOUT-VP即为斩波后的Vos,对于您100kHZ的斩波频率,这个时刻应该是正好处于其中某一相(例如clk=1)也就是一个稳态,那这样得到的Vos和我直接将clk一直为1仿出来的有什么区别呀?

感谢支持!

![图片链接]()

这个是这么回事,我给你画个图你可能就明白了:

查看图片

由于运放存在一个失调电压,这时将它接成单位反馈时,它的输出将不会等于输入,而是会有一定的差距。假设输入是 1.5 V,这时由于失调电压的存在,它的输出将不会是 1.5 V。这里假设失调电压为 0.1 V,此时它的输出将会是 1.6 V。这时给运放加上斩波,如果正常的给斩波运放加上时钟,那么这个运放的输出电压在 clk = 1 的时候为 1.6 V,在 clk = 0 的时候就因该是 1.4 V,最终输出的波形是图(1)中黑线的样子。可以看出输出为一个方波,这时如果在后面加上一个低通滤波器,将这个方波的基频及以上的频率滤掉,只保留其直流项,那么低通滤波器最后的输出电压将会稳定在 1.5 V 附近,上下只有一个小的波动。而 0.9775ms 这个时刻,正好就是处于这个波动的达到一个中间值(约 1.5 V,就是我们期望的输入等于输出)的时刻,如图(1)中的紫色线所示。如果按照你说的将 clk 一直置 1,那么最终运放和低通滤波器的输出电压将一直为 1.6 V,如图(2),这个斩波相当于没用了,输入还是不等于输出,并不能真正消除失调。

明白了,太感谢你了!中秋节快乐!

也祝你中秋节快乐!

您好,我想问一下这个传输门怎么有六个端口,应该怎么接

作者:干饭睡觉真君

原文链接:https://www.analog-life.com/2022/05/montecarlo-simulation-for-chopping-amp-on-cadence-ic-617/

著作权归作者所有。商业转载请联系作者获得授权,非商业转载请保留链接注明出处。

这六个端口分别是:输入、输出、NMOS 的栅极、PMOS 的栅极、NMOS 的衬底(B)、PMOS 的衬底(B)。接法一般是输入输出接传输门想要传输的信号,NMOS 的栅极和 PMOS 的栅极接时钟,NMOS 的衬底(B)和 PMOS 的衬底(B)一个接地一个接电源。具体传输门的内部的结构你可以去一些工艺库里面看一下他们的数字单元库的传输门是怎么做的,看过后基本就明白了。

衬底这么接会不会有体效应的影响?直接接源极可以吗

在 CMOS 工艺下对 PMOS 来说确实可以,但是对 NMOS 来说不行,NMOS 是直接做在 P 衬底上面的,所以 NMOS 的衬底必须接最低电位。

不过一般对于这种数字相关的器件也不会考虑这么多,直接 PMOS 衬底接 VDD,NMOS 接 GND 就行。

好的好的,多谢学长,我也是今年复旦微电子的研究生,啥也不懂。。。

不用这么谦虚(#笑哭),以后可以多交流。如果想学模拟集成电路得话可以给你推荐一下西交大张老师讲的课程,b 站上面就有:西安交大张鸿老师模拟CMOS课程

您好,我又来了。。。我想问一下你说的那个先仿1/f噪声的转角频率进而确定斩波的频率,我现在就是不知道如何确定斩波的频率,有些论文中提到了说斩波频率要大于运放的增益带宽积

这个因该是要看应用的吧,我做这个斩波运放是用在温度传感器的带隙基准中的,斩波的主要的目的是为了消除失调和 1/f 噪声,并且系统最后有一个过采样 ADC 来数字滤波,所以才选了这个频率。你要选的频率因该是需要根据系统架构分析。这里有篇文章你可以参考一下:斩波运放及陷波技术的时域理解

题主,你好,我也用了斩波电路做温度传感器的感温电路的放大器里,但是我后面是sar ADC,用rc滤波会占很大面积,想请教下一般用什么滤波会比较好?

你好,我这边并没有为温度传感器设计过滤波器,因为我们当时后面使用的是 Sigma-Delta ADC,这种 ADC 内部自带数字滤波器,可以消除斩波造成的影响。至于 SAR 可以使用什么滤波器,我们这边做接收机的时候曾经使用过 Tow-Thomas 滤波器,这种结构的滤波器通过使用 OTA 加上少量 RC 组成,并且有一个比较好的滤波效果。

好的,谢谢回复

哈哈,已经看完了,讲的确实很好

你好,我想问一下就是,电路中使用的传输门由clk时钟控制,按理来说应该是一个clk和一个clkq(clk的反向),但是我看原理图里好像没有给CLK取反,当然也有可能是我看错了

这个只要给的信号是对(一个同相一个反相)的就行,名字不重要,我引用的这个原理图里用 CLK 代表同相,CLKB 代表反相时钟。名字只是一个符号,方便理解即可,只要信号加的对工作就不会出问题。

但是仿真原理图里只看到一个时钟输入信号clk,clkB由谁提供呢,一个传输门应该同时提供clk和clkb吧⌇●﹏●⌇

当然是打好 Pin 然后由 Testbench 的电压源提供了。

哦哦好的,打扰了😳

widlar电流源旁边的是启动电路嘛?

是的,我个人比较喜欢这个结构的启动电路,工作比较稳定,而且也能够正常退出。

这种偏置电路一定要加启动电路,很容易不启动,而且跟工艺也有关,我的一个比较器用的这个偏置,公司工艺更新后偏置电路就没启动

是的,这种偏置电路很容易面临启动问题,我这个例子中简单的加了一个启动电路,但是可能也并不完全保险,因为有些启动电路通常 PVT 变化比较大,甚至还和上电速度有关系。

你好请问为什么我跑蒙特的时候,跑dc能plot出直方图,而跑tran就不行呢

抱歉,这个可能和具体的仿真设置有关,所以我目前没办法给你明确的解答,不过你可以试着检查一下输出表达式是否正确以及在蒙特卡洛设置界面上是否选择了保存输出波形,然后你可以选择只跑一个点的蒙卡试一下。

楼主,我想问一下,最后chopper on的时候,是否有人工加入失调,我蒙卡仿真条件基本和您一样,斩波频率100K,时间选取也是0.9975ms,没有加入人工失调,chopp on和chopper off的蒙卡仿真结果一样的,正如一楼所说的,0.9975ms是斩波频率CLK=1的相位,和CLK全为1稳态一样,蒙卡最终结果是一样的。问题就在这个您在文中是否加入人工失调.

你好,这个文章是我大约一年前写的,现在我已经从那个学校毕业了,所以我也没法找到原电路验证你的说法,但是我印象中这个电路是没有人工加入失调的。至于 CLK 以 100 kHz的频率变化和 CLK 一直等于 1 的情况下跑出来的失调一样的情况,这个我最近会抽时间拿一个电路试一下看看。

主要是我对这个文章最后结论有一些疑问,因为在文中没有chopper off的失调电压蒙卡结果,只有chopper on之后的失调电压蒙卡。不清楚这个失调小100多倍的结论是与哪个进行对比的。

哦哦,这个是我描述的不清楚,感谢你指出。这个「失调小 100 多倍」是针对我的博客里之前的一篇文章而言的,具体的文章连接在这里:使用 Cadence IC617 的蒙特卡洛仿真器仿真单端运放的失调电压。现在我已经在这篇文章最后加上了对这个「100 倍」的解释,感谢你的提醒。

如果您有时间验证chopper on和chopper off的失调,麻烦您说一下结果,看是否和我验证的结果一致。

你好,我最近验证了一下,chopper on 和 chopper off 的失调大小确实有明显的区别。但是由于我现在已经登不上之前写这个文章时候用的服务器了,因此只能新搭了一个运放来验证。这是仿真结果图片,你可以看一下:

![Chopper 前后仿真结果对比]()

查看图片

看这个图怎么感觉加了chop之后失调变大了

并没有变大,之前的一篇文章是不加斩波的失调仿真结果,可以看出加了斩波之后失调小了很多。

那您能补充一下这个参数设置和仿真步骤吗,因为我这个chopper on和chopper off的失调没有任何变化,我想对照一下这个错误出在哪里。

你好,我这个蒙特卡洛仿真的步骤就是文章中的步骤。造成你前后仿真结果一直的原因可能是多方面的,比如原理图连接是否正确、时序连接是否正确、仿真设置是否正确以及蒙特卡洛设置是否正确等等。建议你对你的电路进行一个逐步的排查,从电路连接到 DC、Tran 工作状态,再到不带蒙卡的仿真是否正常,再到蒙卡仿真,直到找到你的电路的 Bug。

请问,斩波之后应该会出现很多毛刺,这个该怎么解决呢?

这个我感觉需要看你的系统对毛刺的容忍程度,我这个电路当时只是打比赛,所以没考虑这么多,如果你这里容忍不了斩波很大的毛刺的话我猜或许可以考虑使用电容滤波等方式,可能有所改善。

楼主,我想问下全差分运放的输入失调电压怎么仿真呀,哪都找不到可靠的方法

差分运放的失调我感觉可以这样仿真:把它连接成一个反馈形式,或者把它放在实际的电路中,然后给输出提供一个输入共模电压,然后这时输出就会存在一个差模成分。使用这个差模成分除以电路结构的增益就可以了,用公式表示就是 $\frac{V_{out\_diff}}{A} – V_{in\_diff}$,$V_{out\_diff}$ 是输出差模量,$V_{in\_diff}$是输入差模量,一般为 0,A 是电路结构的增益。按照这个原理搭建 TestBench 就可以了。

是的,已经尝试过,但结果好像不是很准确,但应该是没问题的。

另外,不知道楼主放不方便提供一个联系方式呢,后面还想和你交流一些模拟IC的问题

有用就行哈哈。

可以的,如果有问题想要交流的话可以发送邮件到:absolutezero@stu.xjtu.edu.cn

您说的这个“运放的 1/f 噪声的拐点频率。通过该拐点频率进而可以确定斩波时钟的频率”,运放的拐角频率是怎么仿真呀,不知道该怎么操作求出来,麻烦大侠解答一下

你好,这个拐点频率可以使用 noise 仿真器进行仿真,简单来说就是仿真运放的输出噪声,具体可以参考一下这篇文章:noise仿真方法

谢谢您的回复,这个噪声功率谱曲线仿真我也知道怎么仿的,问题是如何确定1/f噪声频率点呀

这个的话好像很难仿真出具体的数值,我一般都是看输出噪声曲线图上从曲线转为平直的那段线所对应的频率,大体就认为这个是它的拐点频率。这个不用特别准确,只要斩波频率取得比你大体估计的这个频率高就行了。

那看来用仿真器来确定拐点频率,目前来说0没有一个合适可用的方法了,我这边了解到一个根据功率谱手动算的拐角频率,分享出来和博主学习探讨一下,网页我插入不了图片,发您邮箱了

好的,非常感谢!目前看来通过仿真器来计算因该是没有什么特别好的方法了。

方便发我一份您确认拐角频率的方法吗,邮箱xuekang_li@163.com,学习一下,感激不尽

感谢大佬的分享,虽然对斩波结构的理解还是有一点模糊,但是工作原理已经明白了。

斩波频率除了和转角频率相关,应该还和-3dB带宽相关,是f-3dB>2*fchop,您使用这个RC密勒补偿,运放的带宽还能大于斩波频率100kHz吗(除非负载很小或者功率很大?),您还能想起来当时的-3dB带宽是多少吗?

您好,是的,斩波也是该和转角频率有关。如果我没记错的话,这个运放的 -3dB 带宽肯定是大于 200 kHz 的。这个运放由于输出负载电容不是很大(就是 bandgap 上面用作电流镜的两个较小的 PMOS 管),因此密勒补偿电容也不用很大,所以还是有一定的带宽的。

我做了低功耗版本的-3db带宽只有1k不到难不成要用1k以下的斩波频率么

斩波运放的频率因该并不一定必须小于 3dB 带宽,具体可以看一下这一篇文章,里面有提到过频率大于带宽后会发生什么事情。

有个问题想请教一下,我是将chopper运用在带隙基准电路中。chopper频率选取500k,进行PSS+Pnoise仿真,仿真结果显示噪声被调制到了500K(500K处有一个小尖峰),但是1M频率处有一个特别大的尖峰,远超过500K处的尖峰值,5M处也有一个小尖峰。噪声应该被调制到奇频处,也就是500K,1.5M,2.5M…,并且随着频率升高幅值呈现下降的趋势,不知道到底哪里出现了问题,还请指点

抱歉,这个问题我并没有遇到过,不知是不是因为你做的电路结果不是完全差分导致的?

你好,请问如何解决的,我仿真的时候出现了一模一样的问题,就是那个1k斩波,1,3,5,7,9都有逐渐变小的斩波,只是突然在10kHz频率处出现了一个很高的谱线,估计是一模一样的问题

您好 有个问题想请教一下 斩波开关的频率如何确定呢

你好,我这边是通过把斩波频率确定在 1/f 噪声以上的方式来确定的,这样的话就能较好的消除掉 1/f 噪声对电路的影响。

感谢你的回复!

感谢大佬

大佬,我在仿真高压mos管(DEmos管)斩波运放的失调的时候,工艺库中没有失调文件,我按您文章中一样,在跑蒙卡的时候,在输入一段加一个1mV的失调电压,来看一下他对失调的抑制吗?

我觉得可以的,这种方法可以评估出来斩波对失调的抑制能力。

谢谢佬,还有个问题想请教佬,斩波会产生纹波,这个纹波要怎么看出来呢?是跑瞬态吗?把管子换成macro管,然后跑蒙卡瞬态吗?希望佬能回答一下,万分感谢。

是的,就按照你说的方式仿真就可以了。